存储器大容量存储

china.

xilinx.

com1白皮书:UltraScale+器件WP477(v1.

0)2016年6月14日UltraRAM:在UltraScale+器件上集成嵌入式存储器取得突破性成功UltraRAM是UltraScale+系列中最新的存储器模块,能实现高达500Mb的总片上存储容量,相当于赛灵思28nmFPGA片上存储器容量的6倍.

摘要传统的FPGA和SoC包含的片上存储器以blockRAM和分布式RAM的形式存在.

由于器件能以更高数据速率处理更多数据,因此越发需要将数据缓冲或存储在靠近处理器的位置.

UltraScale+系列中的新产品是一款容量更大的称为UltraRAM的灵活存储器模块.

UltraRAM模块可级联在一起构成更大的片上存储器.

在设计中使用UltraRAM很简单,因为赛灵思提供了所有必要工具,利用这些工具可以在设计中集成功能强大的最新模块.

2016年赛灵思公司版权所有.

Xilinx、赛灵思标识、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq及本文提到的其它指定品牌均为赛灵思在美国及其它国家的商标所有其他商标均为各自所有者的财产.

china.

xilinx.

com2缓冲与存储的需求增加UltraScale+FPGA和MPSoC能够传输和处理的数据比前一代器件多得多.

最大的VirtexUltraScale+FPGA(即VU13P)包含128个数据速率高达32.

75Gb/s的GTY收发器,以及超过11,000个工作频率接近900MHz的DSPSlice.

这样可得到8.

4Tb/s串行带宽和21TMAC/s的信号处理速度,因此,片上存储器也需要实现同样的增长,以使系统能够有效地缓冲处理前进入的数据和处理后流出的数据.

到达(进入)UltraScaleFPGA器件,blockRAM和分布式RAM可作为快速和高效的片上存储器.

为了成功处理数百兆位的数据,通常需要使用外部存储器,例如DDR4、DDR3或RLDRAM3.

UltraScale+系列产品则采用一种新的存储方法.

UltraRAM是一种大容量、重量轻的存储器模块,使UltraScale+器件具备500Mb以上的高能效、低成本片上数据存储器,相当于赛灵思28nmFPGA片上存储器的6倍.

灵活的级联功能使得UltraRAM模块能够采用多种配置——既可单独使用,也可在器件中将所有模块连接在一起使用.

这使得用户能够构建大小适合应用需求的存储器阵列,并省去一些PCB上的外部存储器组件,例如QDRSRAM.

UltraRAM细节与特性赛灵思很多代的FPGA和SoC都采用分列架构,将不同资源列并排布置在一起.

列的数量和高度直接决定FPGA或SoC的尺寸和容量.

大多数KintexUltraScale+和ZynqUltraScale+器件都包含一列UltraRAM;高端VirtexUltraScale+FPGA则包含多达5列UltraRAM.

UltraRAM可在设计中作为单个288Kb存储器,或者连接在一起构成更大的RAM阵列.

相同列中的所有UltraRAM都可连接在一起,通过专用的级联路由传送地址、数据和控制信号.

在KintexUltraScale+和ZynqUltraScale+器件中,级联得到的RAM阵列可高达36Mb,在VirtexUltraScale+器件中可达到22.

5Mb.

VirtexUltraScale+系列中,所有UltraRAM列都可通过光纤路由连接在一起,在最大器件中可构成容量达360Mb的存储器阵列.

每个UltraRAM模块都是一个双端口同步288KbRAM,采用深度为4,096、宽度为72位的固定配置.

端口A和端口B共享相同时钟信号.

在外部时钟的单个周期内,端口A操作总是在端口B操作之前完成.

每个端口在每个时钟周期都可独立执行一个读操作或一个写操作.

当两个端口在相同时钟周期内以相同地址(即地址冲突)执行写操作时,端口B的写操作有效,因为端口A上的写操作被覆盖.

当端口A执行读操作,而端口B以相同地址执行写操作时,端口A获得存储器阵列中的旧数据,然后端口B上的新数据被写到存储器阵列.

当端口A执行写操作,端口B执行读操作时,端口A上的新数据被写入存储器阵列,新数据也被读到端口B.

对于每个端口,当执行写操作时,该端口的读输出不变,保持之前的值.

china.

xilinx.

com3每个UltraRAM存储器阵列的内容都被每个端口上的汉明码单误差校正双误差检测(SECDED)ECC码保护,以确保数据完整性.

启动ECC后,UltraRAM提供64位宽的被保护数据字.

UltraRAM的SECDEDECC代码与blockRAM的兼容.

这样可实现端到端数据保护方案,即在一个存储器输入端进行编码的数据,在下游存储器输出端对其进行解码之前,可在多个流水线级、存储器类型和/或逻辑上保持受保护状态.

UltraRAM每两个端口包含多达四个流水线级,并可针对1-4个时钟周期的时延进行配置.

当通过级联UltraRAM搭建较大的RAM阵列时,时延取决于所用UltraRAM的数量(即阵列的大小以及目标工作频率).

功耗降低UltraRAM提供各种内置功能以最大化功率效率,通常无需用户干预.

这些功能包括:将设计中不用的UltraRAM断电自动对不使用的流水线寄存器进行时钟门控当UltraRAM长时间不使用时,使其进入休眠模式UltraRAM可通过手动或自动进入休眠模式.

用户可以访问UltraRAM的SLEEP端口.

激活SLEEP时,UltraRAM从下个时钟周期开始进入休眠模式.

休眠模式下,UltraRAMSRAM存储器的外设逻辑断电,但SRAM保持加电并保留其中的内容.

每个UltraRAM都包含相应的电路用来预测和识别接下来N个周期内模块是否会被使用,如果不使用,那么在未使用时间足够长之后,模块会被送入休眠模式.

这种自动休眠模式使用休眠端口,利用内置的控制逻辑来检查将即将输入的地址和使能信号的状态.

AUTO_SLEEP_LATENCY属性决定地址和使能信号需要比其他输入信号提前多久到达.

该信息用来确定是否有足够的时间使单个UltraRAM进入休眠模式并在下个活动之前将其唤醒.

在设计中使用UltraRAMUltraScale+产品组合使用赛灵思的VivadoDesignSuite.

设计工具提供一系列代码模板,可帮助用户成功锁定器件内的可用资源.

有三种方法可以在RTL设计中使用UltraRAM:编写代码以调用存储器;实例化器件原语;使用最近添加的赛灵思参数化宏(XPM).

大多数用户都熟悉调用和实例化.

VivadoDesignSuite包含调用模板,所在位置:模板→VHDL/Verilog→综合构建→编码实例→RAMchina.

xilinx.

com4在VivadoDesignSuitev2016.

1.

中,用户必须指定ramstyle="ultra"才能明确指示Vivado综合使用UltraRAM.

如果用户需要对UltraRAM模块的连接具有最终控制权,应使用以下位置的器件原语:模板>VHDL/Verilog>器件原语实例化>Kintex/VirtexUltraScale+>BLOCKRAM>URAM尽管能让用户对单个组件的连接实现最严格的控制,但如果采用很多组件并有很多端口和信号,那么这种方法很快就会变得很费劲.

要在RTL设计中采用UltraRAM,第三种方法是XPM:模板→VHDL/Verilog→赛灵思参数化宏(XPM)→存储器(XPM_MEMORY)→RAMXPM是一种用来根据用户指定要求创建RAM和ROM结构的最新工具.

用户可在XPM代码中指定多个类属,包括存储器大小、时钟模式、ECC模式等.

这些要求随后被Vivado综合转化为适当的存储器阵列尺寸和风格.

在VivadoDesignSuitev2016.

1中,用户必须在MEMORY_PRIMITIVE类属上指定值UltraRAM,以明确指示Vivado综合使用UltraRAM.

创建存储器阵列UltraRAM架构扩展性非常强,允许很多个UltraRAM模块高效地连接在一起,以构成深逻辑存储器,仅使用很少甚至无需架构资源,而且访问时延相对较短.

每个UltraRAM包含所有必要的逻辑,用以将相同列中相邻UltraRAM模块之间的全部输入以及输出接口进行完全级联,并有选择性地进行流水线化.

此外,每个UltraRAM都包含每端口上的附加逻辑和控制输入,以独立确定UltraRAM模块阵列中经过的读或写事务处理是否针对本地阵列,还是应该被忽略掉.

这种分布式的决策逻辑能实现灵活而且低开销的扩展性.

当设计中的指定存储器阵列需要一个以上UltraRAM模块时,必须决定如何将多个UltraRAM连接在一起.

有两个选择分别是:使用一个列中的所有UltraRAM,或者使用多列阵列中的UltraRAM.

如果在一个列中构建UltraRAM阵列,那么用来级联UltraRAM的所有必要路由都包含在该列中,使工具能够充分利用所提供的专用资源.

见图1.

china.

xilinx.

com5读数据ECC状态读地址和控制写地址和控制写数据图1:在一个列中级联的UltraRAM如果设计要求决定了多列阵列更加适合,例如,如果所需的阵列大于单个列的容量,那么需要创建多列阵列(见图2).

这种情况下,需要用一些架构资源将多个列连接在一起.

最大可实现频率以及多列阵列中的访问时延取决于阵列尺寸、所用列的数量以及其他设计因素(例如UltraRAM列之间有多少架构资源被设计的其他部分使用).

china.

xilinx.

com6读数据ECC状态读地址和控制写地址和控制写数据图2:多列UltraRAM阵列当创建UltraRAM阵列时,地址、控制和写数据信号被提供至阵列的左下角,数据从阵列的右上角读取.

这样能确保,通过对固定大小的阵列进行恰当流水线化后,从任何地址读取任何数据所产生的时延总相同.

与每个UltraRAM自身可提供的64位ECC保护或72位非ECC保护字宽相比,宽数据或控制路径设计需要更高的总线带宽.

这种情况下,可以并列使用多个相同的UltraRAM模块实例或以上描述的级联结构来构建非常高效的宽字数据存储结构.

china.

xilinx.

com7寄存器和流水线化每个UltraRAM包含多个输入和输出寄存器,如图3所示,其中有一些是可选的,取决于配置情况和所需的功能.

存储器图3:UltraRAM寄存器IREG、OREG和OREG_ECC寄存器根据用户所需的存储器功能进行激活.

此外,当把多个UltraRAM级联在一起时使用的寄存器为:IREG_PRE和REG_CAS.

当把多个UltraRAM连接在一起时需要遵守一些规则,以保持最大工作频率:单列阵列中的第一个实例或多列阵列每个列中的第一个实例都必须使用IREG_PRE寄存器.

如果设计中需要,OREG和/或OREG_ECC寄存器应针对阵列中的所有UltraRAM一直启用.

必须每经过四个UltraRAM模块激活REG_CAS寄存器.

单列阵列中的最后一个实例或者多列阵列每列中的最后一个实例必须使用REG_CAS寄存器.

如果阵列垂直跨越多个时钟区域,那么需要在时钟区域边界两侧提供附加流水线级.

每个时钟区域的每列上有16个UltraRAM.

如需了解UltraRAM模块的更多信息和详细框图,请参考UG573《UltraScale架构存储器资源用户指南》的第二章.

china.

xilinx.

com8迁移到UltraRAM用户一定要知道所选目标器件中不同存储器资源的数量.

有些情况下,用户最开始可以针对只有blockRAM的器件,但设计最终将会针对包含UltraRAM的器件.

这种情况下,用户需要了解UltraRAM的特性,并编写代码以利用blockRAM和UltraRAM中的特性.

这样,工具就可使用目标器件中可使用的UltraRAM,而且,当改用不同器件时用户不必重新设计.

表1给出了不同UltraScale+系列中UltraRAM的数量.

在VirtexUltraScale+器件中,可将所有UltraRAM连在一起,以构成容量高达360Mb的多列阵列;不过,也可实现更为常用的10Mb-144Mb范围的多实例使用模型.

表1:UltraScale+产品组合中的UltraRAM资源系列KintexUltraScale+VirtexUltraScale+ZynqUltraScale+UltraRAM0–128320-1,2800-120UltraRAM(Mb)0-3690-3600-36列高(Mb)0-3618.

0或22.

50-36所有UltraScale+器件还包含可实现较小存储器的blockRAM和分布式RAM,从而在VU13P中实现总容量超过500Mb的片上存储器.

DS890,《UltraScale架构和产品简介》给出了器件资源方面的更多详情.

如果所选的器件中有UltraRAM,应该将其用作144Kb或更大的存储器.

替代外部存储器组件高达360Mb的UltraRAM几乎可配置成无数种方式,因此会有很多种使用模式.

常见的UltraRAM使用模式是如果不实现在外部存储器(例如QDRSRAM)中,可以将存储器整合在FPGA或MPSoC中.

片上存储器的优势在于可采用所需要的容量大小,而不是存储器厂商提供的大小;而且存储器在逻辑上非常接近设计中用来缓冲或存储数据的位置.

此外,为了与外部存储器进行连接,数据必须通过存储器接口或控制器,并且通过FPGA/MPSoC上的I/O引脚,而且外部存储器组件会给系统增加很多功耗.

通过以UltraRAM的方式在片上实现大容量存储,这样可消除FPGA/MPSoC的I/O以及外部存储器的I/O产生的功耗.

china.

xilinx.

com9输入多播每个UltraRAM端口都可确定级联模式中的事务处理是否属于局部存储器阵列.

该功能可用来实现动态的事务处理级写单播、多播和广播存储器结构.

这种结构可以构成高效输出缓冲存储器开关的基础.

有一个UltraRAM存储器端口专门用来写,另一个专门用来读.

所有UltraRAM模块的写端口都采用每模块唯一的独热编码SELF_ADDR和相配的独冷编码SELF_MASK值配置为连续级联形式.

每个写事务处理都可以被送到单个、多个或所有UltraRAM模块,方法是设置一个或多个相应的全局/高地址位,以匹配所有目标模块的SELF_ADDR属性的logical-OR.

所有UltraRAM模块的读端口都是非级联的,能够让单个写事务处理传播到多个消费模块.

每个UltraRAM模块代表一个消费模块的缓冲要求.

要获得更大的存储容量,可将每个UltraRAM模块改成N个UltraRAM模块级联成的消费模块.

假设C个消费模块从C个逻辑存储器(每个深度为N个UltraRAM模块)并行读取,那么写端口需要一个包含所有C*N个UltraRAM模块的连续级联,而读端口需要C个独立的级联,每个深度为N个UltraRAM.

图4给出了这样一种配置,其中每个消费模块有四个输出,每个输出需要一个UltraRAM模块作为缓冲,并有两个样本多播事务处理分别针对UltraRAM模块0和1以及1和3.

china.

xilinx.

com10输出端口=多播写数据包流图4:输入多播结论每个设计都需要和使用这样或那样的存储器.

将大容量、灵活的UltraRAM模块添加到UltraScale+产品系列后,为用户提供的片上存储器容量比以往任何器件或竞争器件都要大.

由于模块可连接在一起构成不同大小的存储器阵列,这样用户就能在设计中在需要的位置构建理想的存储器解决方案,消除了使用外部SRAM组件所带来的功耗和电路板复杂性.

china.

xilinx.

com11修订历史下表列出了本文档的修订历史:日期版本修订描述2016年06月14日v1.

0赛灵思初始版本免责声明本文向贵司/您所提供的信息(下称"资料")仅在选择和使用赛灵思产品时供参考.

在适用法律允许的最大范围内:(1)资料均按"现状"提供,且不保证不存在任何瑕疵,赛灵思在此声明对资料及其状况不作任何保证或担保,无论是明示、暗示还是法定的保证,包括但不限于对适销性、非侵权性或任何特定用途的适用性的保证;且(2)赛灵思对任何因资料发生的或与资料有关的(含对资料的使用)任何损失或赔偿(包括任何直接、间接、特殊、附带或连带损失或赔偿,如数据、利润、商誉的损失或任何因第三方行为造成的任何类型的损失或赔偿),均不承担责任,不论该等损失或者赔偿是何种类或性质,也不论是基于合同、侵权、过失或是其他责任认定原理,即便该损失或赔偿可以合理预见或赛灵思事前被告知有发生该损失或赔偿的可能.

赛灵思无义务纠正资料中包含的任何错误,也无义务对资料或产品说明书发生的更新进行通知.

未经赛灵思公司的事先书面许可,贵司/您不得复制、修改、分发或公开展示本资料.

部分产品受赛灵思有限保证条款的约束,请参阅赛灵思销售条款:http://china.

xilinx.

com/legal.

htm#tos;IP核可能受赛灵思向贵司/您签发的许可证中所包含的保证与支持条款的约束.

安全保护功能,不能用于任何需要专门故障安全保护性能的用途.

如果把赛灵思产品应用于此类特殊用途,贵司/您将自行承担风险和责任.

请参阅赛灵思销售条款:http://china.

xilinx.

com/legal.

htm#tos.

汽车应用免责申明赛灵思产品并非为故障安全保护目的而设计,也不具备此故障安全保护功能,不能用于任何需要专门故障安全保护性能的用途,比如与下列有关的用途:(1)安全气囊设置;(2)车辆控制,除非在该赛灵思产品中具备故障安全保护或者额外功能(但不包括对安装在赛灵思设备中用于执行该等额外功能的软件的使用)且会对操作人员操作失误发出警告信号;或者(3)可能会导致死亡或者人身损害的用途.

客户应当自行承担因赛灵思产品被用于该等用途而产生的全部风险和责任.

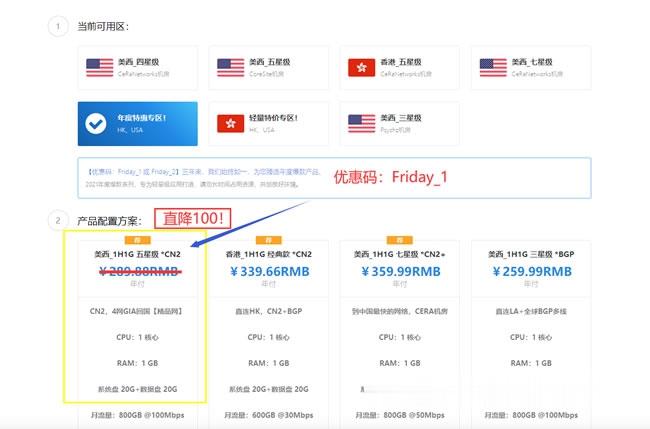

极光KVM美国美国洛杉矶元/极光kvmCN7月促销,美国CN2 GIA大带宽vps,洛杉矶联通CUVIP,14元/月起

极光KVM怎么样?极光KVM本月主打产品:美西CN2双向,1H1G100M,189/年!在美西CN2资源“一兆难求”的大环境下,CN2+大带宽 是很多用户的福音,也是商家实力的象征。目前,极光KVM在7月份的促销,7月促销,美国CN2 GIA大带宽vps,洛杉矶联通cuvip,14元/月起;香港CN2+BGP仅19元/月起,这次补货,机会,不要错过了。点击进入:极光KVM官方网站地址极光KVM七月...

BGPTO独服折优惠- 日本独服65折 新加坡独服75折

BGPTO是一家成立于2017年的国人主机商,从商家背景上是国内的K总和有其他投资者共同创办的商家,主营是独立服务器业务。数据中心包括美国洛杉矶Cera、新加坡、日本大阪和香港数据中心的服务器。商家对所销售服务器产品拥有自主硬件和IP资源,支持Linux和Windows。这个月,有看到商家BGPTO日本和新加坡机房独服正进行优惠促销,折扣最低65折。第一、商家机房优惠券码这次商家的活动机房是新加坡...

萤光云(13.25元)香港CN2 新购首月6.5折

萤光云怎么样?萤光云是一家国人云厂商,总部位于福建福州。其成立于2002年,主打高防云服务器产品,主要提供福州、北京、上海BGP和香港CN2节点。萤光云的高防云服务器自带50G防御,适合高防建站、游戏高防等业务。目前萤光云推出北京云服务器优惠活动,机房为北京BGP机房,购买北京云服务器可享受6.5折优惠+51元代金券(折扣和代金券可叠加使用)。活动期间还支持申请免费试用,需提交工单开通免费试用体验...

-

cm域名注册cm域名是什么含义?价格是多少?注册地址是多少?有什么投资价值?中国域名注册中国十大域名注册商网站服务器租用个人网站服务器租用一年多少钱便宜的虚拟主机低价虚拟主机那种类型的好呢?云服务器租用云服务器租用需要注意哪些方面香港虚拟空间最好的香港虚拟主机是哪家?jsp虚拟空间JSP虚拟目录及虚拟路径的配置方法免费网站空间哪里有永久免费的网站空间?免费网站空间申请需要一个免费的网站空间申请地址。虚拟主机99idc网站后台织梦系统重装、空间转移、及上传技巧有哪些?