REFCLK200M_HSTLavtt.info

avtt.info 时间:2021-04-06 阅读:()

ADM-VPX3-7V2UserManualDocumentRevision:1.

922ndAugust2016ADM-VPX3-7V2UserManualV1.

9-22ndAugust20162016CopyrightAlphaDataParallelSystemsLtd.

Allrightsreserved.

ThispublicationisprotectedbyCopyrightLaw,withallrightsreserved.

Nopartofthispublicationmaybereproduced,inanyshapeorform,withoutpriorwrittenconsentfromAlphaDataParallelSystemsLtd.

HeadOfficeAddress:4WestSilvermillsLane,Edinburgh,EH35BD,UKTelephone:+441315582600Fax:+441315582700email:sales@alpha-data.

comwebsite:http://www.

alpha-data.

comUSOffice3507RingsbyCourtSuite105,Denver,CO80216(303)9548768(866)8209956tollfreesales@alpha-data.

comhttp://www.

alpha-data.

comAlltrademarksarethepropertyoftheirrespectiveowners.

ADM-VPX3-7V2UserManualV1.

9-22ndAugust2016TableOfContents1Introduction11.

1KeyFeatures11.

2References&Specifications22Installation32.

1SoftwareInstallation32.

2HardwareInstallation32.

2.

1SystemRequirements32.

2.

2CoolingRequirements33FunctionalDescription43.

1Overview43.

1.

1SwitchDefinitions53.

1.

2LEDDefinitions63.

2VPXP0Interface73.

2.

1MVMRO73.

2.

2SYSRESET#73.

2.

3AUXCLK73.

2.

4REFCLK73.

3VPXP2GPIO73.

3.

1LVDS73.

3.

2CMOS73.

4JTAGInterface83.

4.

1On-boardInterface83.

4.

2VPXInterface83.

4.

3JTAGVoltages83.

5Clocks93.

5.

1200MHzReferenceClock(REFCLK200M)103.

5.

2250MHzReferenceClock(REFCLK200M)103.

5.

3ProgrammableClocks(LCLK,PROGCLK0-4)113.

5.

4FMC-CarrierMGTClock(MGTCLK_M2C)113.

5.

5FMC-CarrierSignalClocks(GCLK_M2C)113.

5.

625MHzSource113.

6FlashMemory123.

7Configuration133.

7.

1Power-UpSequence133.

7.

2Bridge-LessMode133.

8HealthMonitoring143.

8.

1AutomaticTemperatureMonitoring153.

8.

2MicrocontrollerStatusLEDs153.

9LocalBus163.

10TargetFPGA163.

10.

1TargetFPGACharacteristics163.

10.

2I/OBankVoltages163.

10.

3TargetMGTLinks173.

11MemoryInterfaces183.

12FMCInterfaceandFront-PanelI/O19AppendixAP1PinAssignments21A.

1DataPlane(P1Wafers1-4)21A.

2Data/ExpansionPlane(P1Wafers5-8)21A.

3Expansion/UserPlane(P1Wafers9-14)22A.

4ControlPlane(P1Wafers15-16)22ADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixBP2PinAssignments23B.

1GPIO24s/12d+8s(P2Wafers1-6)23B.

2MGTLanes20d(P2Wafers7-16)24AppendixCFMCPinAssignments25C.

1GPIOPins25C.

2ClockPins27C.

3MGTPins28ListofTablesTable1References2Table2SwitchDefinitions5Table3LEDDefinitions6Table4REFCLK200MConnections10Table5REFCLK250MConnections10Table6PROGCLKConnections11Table7MGTCLK_M2CConnections11Table8VoltageandTemperatureMonitors14Table9TemperatureLimits15Table10StatusLEDDefinitions15Table11TargetFPGACharacteristics16Table12TargetFPGAIOBanks16Table13TargetMGTLinks17Table14MaximumMemorySpeeds18Table15DataPlane(P1Wafers1-4)21Table16Data/ExpansionPlane(P1Wafers5-8)21Table17Expansion/UserPlane(P1Wafers9-14)22Table18ControlPlane(P1Wafers15-16)22Table19RGMIIto1000Base-XPHY22Table20GPIO24s/12d+8s(P2Wafers1-6)23Table21MGTLanes20d(P2Wafers7-16)24Table22GPIOPins25Table23ClockPins27Table24MGTPins28ListofFiguresFigure1ADM-VPX3-7V2ProductPicture1Figure2ADM-VPX3-7V2AirCooled3Figure3ADM-VPX3-7V2BlockDiagram4Figure4LEDLocations6Figure5JTAGHeaderJ38Figure6JTAGBoundaryScanChain8Figure7Clocks9Figure8FlashMemoryMap12Figure9DRAMBanks18ADM-VPX3-7V2UserManualV1.

9-22ndAugust20161IntroductionTheADM-VPX3-7V2isahigh-performanceXMCforapplicationsusingVirtex-7FPGAsfromXilinx.

ThiscardsupportsVirtex-7devicesavailableintheFF(G),FH(G),andFL(G),1761package.

TheADM-VPX3-7V2includesaseparateFPGAwithaPCIebridgedevelopedbyAlphaData.

Usingaseparatedeviceallowshighperformanceoperationwithouttheneedtointegrateproprietarycoresintheuser(target)FPGA.

Withthereleaseof7seriesFPGAboards,AlphaDatahasintroducedanewbuildoptiontoallowthemezzaninecardtobeassembledwithoutthebridgetoreducepowerandcost.

TheADM-VPX3-7V2isavailableinair-cooledandconduction-cooledconfigurations(with2LevelMaintenancecompatibility).

ViewtheADM-VPX3-7V2OrderingInfotabatADM-VPX3-7V2ProductPageonwww.

alpha-data.

com.

Figure1:ADM-VPX3-7V2ProductPicture1.

1KeyFeaturesKeyFeaturesOpenVPXComplianceList3UOpenVPX,complianttoVITAStandard46.

0and65Dedicated4-lanePCI-ExpressGen2interfacewithhigh-performanceDMAcontrollers4additionalPCI-ExpresscompliantGTXlinksbetweenuserFPGAandOpenVPXDataPlane4laneExpansionportcomplianttoOpenVPX2Controlplaneconnections,onetouserFPGA,onetoBridgeP2ConnectorcomplianttoVita46.

9X24S+X8D+X12DSupportforVirtex-7FPGAinFF(G),FH(G),andFLG(G)1761package4independentbanksofDDR3-1600SDRAM,512MB/bank,2GBtotal(4GBoption)FMCfrontpanelinterfacecompliantwithVita57.

1utilizingallIOandallHigh-Speedlinks.

1PPSCapableviaOpenVPXAUXCLKClocksynchronizationwithOpenVPXREFCLKOn-boardprogrammableclocksenablingmultipleprotocolstobeimplementedontheuserFPGA'shigh-speedlinksVoltageandtemperaturemonitoringAir-cooled,conduction-cooled,and2LevelMaintenanceconfigurationsavailableSLT3-PAY-2F1F2U-14.

2.

1Page1Introductionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SLT3-PAY-1F2F2U-14.

2.

2SLT3-PAY-2F2U-14.

2.

3SLT3-PAY-1F1F2U-14.

2.

4SLT3-PAY-1D-14.

2.

6SLT3-PAY-2F-14.

2.

7SLT3-PAY-1F4U-14.

2.

8SLT3-PAY-8U-14.

2.

9SLT3-PER-2F-14.

3.

1SLT3-PER-1F-14.

3.

2SLT3-PER-1U-14.

3.

31.

2References&SpecificationsANSI/VITA46.

0VPXBaselineStandard,October2007,VITA,ISBN1-885731-44-2ANSI/VITA46.

9PMC/MXCRearI/OFabricSignalMappingon3Uand6UVPXModulesStandard,November2010,VITA,ISBN1-885731-63-9ANSI/VITA48.

2MechanicalSpecificationsforMicrocomputersUsingREDIConductionCoolingAppliedtoVITAVPX,July2010,VITA,ISBN1-885731-60-4ANSI/VITA57.

1FPGAMezzanineCard(FMC)Standard,February2010,VITA,ISBN1-885731-49-3ANSI/VITA65OpenVPXSystemSpecification,June2010,VITA,ISBN1-885731-58-2Table1:ReferencesPage2Introductionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20162Installation2.

1SoftwareInstallationPleaserefertotheSoftwareDevelopmentKit(SDK)installationCD.

TheSDKcontainsdrivers,examplesforhostcontrolandFPGAdesignwithcomprehensivehelponapplicationinterfacing.

2.

2HardwareInstallation2.

2.

1SystemRequirementsTheADM-VPX3-7V2isa3UOpenVPXcompliantFPGAcardwithFMCfrontIOinterface.

TousetheAlphaData'spowerfulAPIanddrivers,thesystemcontrollermustbecapableofdrivingthePCIelanestotheBridge.

TheADM-VPX3-7V2alsoutilizestheOpenVPX1000Base-Xcontrollines,thoughthisimplementationislefttotheuser.

P2complieswithVita46.

9X24S+X8D+X12Duserdefinedpinconfigurationwithanadditional8connectionstoP2RowG.

TheX24scanbeconfiguredaseither24songleendedsignalsat3.

3Vor12LVDSpairs(butnotboth).

TheeightuserdefinedsingleendedconnectionsinrowGare3.

3Vcompliantandcanbeisolatedfromthebackplaneviaonboardswitches.

AlphaDataoffersaRearTransitionModule(RTM)thatbreaksoutallP2IOandP1controllanesforuseinlabanddevelopmentenvironments(Partnumber:ADM-VPX3-7V2-RTM).

TheADM-VPX3-7V2canbeconfiguredtoeitherutilize5Vor12Vasthemainpowersource.

Thedefaultbuilduses5V,contactsales@alpha-data.

comfordetailsonthe12Vbuildoption.

2.

2.

2CoolingRequirementsThepowerdissipationoftheboardishighlydependentontheTargetFPGAapplication.

ApowerestimatorspreadsheetisavailableonrequestfromAlphaData.

ThisshouldbeusedinconjunctionwithXilinxpowerestimationtoolstodeterminetheapproximatecurrentrequirementsforeachpowerrail.

Theboardissuppliedwithapassiveaircooledorconductioncooledheatsinkaccordingtotheordernumbergivenattimeofpurchase.

Itistheusersresponsibilitytoensuresufficientairflowforaircooledapplicationsandappropriatemetalworkforconductioncooledapplications.

TheboardfeaturessystemmonitoringthatmeasurestheboardandFPGAtemperature.

Italsoincludesaself-protectionmechanismthatwillclearthetargetFPGAconfigurationifanover-temperatureconditionisdetected.

SeeSectionHealthMonitoringforhealthmonitoringdetails.

Figure2:ADM-VPX3-7V2AirCooledPage3Installationad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163FunctionalDescription3.

1OverviewFigure3:ADM-VPX3-7V2BlockDiagramPage4FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

1.

1SwitchDefinitionsThereisasetofeightDIPswitchesplacedonthebottomoftheboard.

TheirfunctionsaredescribedinTableSwitchDefinitions.

Note:AllswitchesareOFFbydefault.

FactoryConfigurationswitchmustbeintheOFFpositionfornormaloperation.

SwitchRef.

FunctionONStateOffStateSW1-1P2LVDS24sonP2useCMOS24sonP2useLVDSSW1-2InternalOscillatorUseVPXREFCLKUseInternalOscillatorsourceSW1-3BridgeBypassBridgeFPGAisbypassed-PCIelanes(3:0)areconnecteddirectlytotheuserFPGA.

BridgeFPGAisused.

PCIelanes(3:0)areconnectedtothebridge.

SW1-4FlashBootInhibitTargetFPGAisnotconfiguredfromonboardflashmemory.

TargetFPGAisconfiguredfromon-boardflashmemory.

SW1-5VPXJTAGConnectJTAGchaintoP0IsolateJTAGchainfromP0SW1-6E-FuseEnableE-Fuseprogrammingvoltage(VccEFuse=2.

5V)DisableE-Fuseprogrammingvoltage(VccEFuse=0V)SW1-7FactoryConfiguration-NormalOperationSW1-8Bridge-LessModeBridge-LessModeActive-UserbitstreamloadedfromSPIflashPCIeBridgeModeActive-UserbitstreamloadedfromBridgeTable2:SwitchDefinitionsPage5FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

1.

2LEDDefinitionsThepositionanddescriptionoftheboardstatusLEDsareshowninFigureLEDLocations:Figure4:LEDLocationsComp.

Ref.

FunctionONStateOffStateD11(Amber)MVMROInhibitwritestonon-volatilememoriesEnablewritestonon-volatilememoriesD12(Green)Status0SeesectionMicrocontrollerStatusLEDsERRORD13(Red)Status1SeesectionMicrocontrollerStatusLEDsERRORD14(Green)BridgeDoneBridgeFPGAisconfiguredBridgeFPGAisunconfiguredD15(Green)TargetDoneTargetFPGAisconfiguredTargetFPGAisunconfiguredD16(Amber)XMCJTAGJTAGchainconnectedtoP0JTAGchainisisolatedfromP0D17(Amber)BridgeBypassBridgeFPGAisbypassed-PCIelanes(3:0)directtouserFPGABridgeFPGAisused.

PCIelanes(3:0)areconnectedtothebridge.

D18(Amber)Bridge-LessTargetisconfiguredbySPImemoryTargetisconfiguredbyBridgeD5(Green)ETH1LED[0]LinkNoLinkD6(Green)ETH2LED[2]LinkNoLinkD7(Amber)ETH1LED[1]ReceiveNoReceiveD8(Amber)ETH2LED[1]ReceiveNoReceiveD9(Green)ETH1LED[2]LinkNoLinkD10(Green)ETH2LED[0]LinkNoLinkTable3:LEDDefinitionsPage6FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

2VPXP0Interface3.

2.

1MVMRONon-VolatileMemoryReadOnly.

Thissignalisaninputfromthesystem.

Whenasserted(high),allwritestonon-volatilememoriesareinhibited.

ThisisindicatedbytheAmberLED,D7.

Thissignalcannotbeinternallydrivenorover-ridden.

AbufferedversionofthesignalisconnectedtothetargetFPGA.

3.

2.

2SYSRESET#XMCResetIn.

Thissignalisanactivelowinputfromthesystem.

Whenasserted,thebridgeFPGAwillbereset.

ThisalsoactsandPCIReset.

TheSYSRESET#signalistranslatedto1.

8VlevelsandconnectedtothetargetFPGAatpinAF30.

3.

2.

3AUXCLKAuxiliaryClock.

ThisclockisadirectinputtothetargetFPGA.

InOpenVPXthisclocklineisusedfor1PPSsynchronizationsignaling.

AUXCLKislimitedto1.

8VbyaquickswitchandthepreferedsignalingstandardisLVDS.

AUXCLK_PisconnectedtoTargetFPGAMRCCpinG14AUXCLK_NisconnectedtoTargetFPGAMRCCpinG133.

2.

4REFCLKReferenceClock.

Thisclockisaninputtotheonboardclockdistributionandgenerationsystem.

The50MHzdefinedinOpenVPXcanbeusedtoalignallsystemclocks.

Alternativelyanonboard50MHzreferencecanbegeneratedasshowninTableSwitchDefinitions.

3.

3VPXP2GPIO3.

3.

1LVDSWhenSW1-1isOFF,theGPIOonP2iscompatiblewith1.

8VsignalingsuchasLVDSand1.

8Vsingleendedsignals.

Thesesignalsarerouteddifferentiallyasshowninthepinouttablesintheappendix.

TheFPGAisprotectedfrominappropriatesignallevelsbyanNXP74CBTLVD3861whichisalowresistancequickswitchthatclampsat1.

8Vineitherdirection,butcanacceptupto3.

3Vonaninput.

3.

3.

2CMOSWhenSW1-1isON,theGPIOonP2iscompatiblewith3.

3VsignalingsuchasTTLandCMOS.

ThesignalsarepassedthroughaTITXS0108ERGYRopen-drain,push-pull,compatibleautodirectionsensingleveltranslator.

ThisprotectstheFPGAfromhighervoltagesonthebackplanewhileallowingittocommunicateat3.

3Vlevels,compliantwithCMOSandTTLvoltages.

Theleveltranslatorhasapropagationdelayof5.

7nsmaxandachannel-to-channelskew(withinapackage)of1ns.

Therefore,itisonlysuitableforratesupto~50Mb/sPage7FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

4JTAGInterface3.

4.

1On-boardInterfaceAJTAGboundaryscanchainisconnectedtoheaderJ3.

ThisallowstheconnectionoftheXilinxJTAGcableforFPGAdebugusingtheXilinxChipScopetools.

TheJTAGHeaderpinoutisshowninFigureJTAGHeaderJ3:Figure5:JTAGHeaderJ3ThescanchainisshowninFigureJTAGBoundaryScanChain:Figure6:JTAGBoundaryScanChainIftheboundaryscanchainisconnectedtotheinterfaceattheVPXbackplane(SW1-5isON),headerJ3shouldnotbeused.

3.

4.

2VPXInterfaceTheJTAGinterfaceontheVPXbackplaneisnormallyunused.

WhenSW1-5isOFF(default),allJTAGsignalstoP0areleftfloating.

TheJTAGinterfacecanbeconnectedtotheVPXBackplane(throughlevel-translators)byswitchingSW1-5ON.

SeeTableSwitchDefinitions3.

4.

3JTAGVoltagesTheon-boardJTAGscanchainuses1.

8V.

TheVccsupplyprovidedonJ3totheJTAGcableis+1.

8Vandisprotectedbyapolyfuseratedat350mA.

3.

3VsignalsmustnotbeusedatheaderJ3.

TheJTAGsignalsattheXMCinterfaceuse3.

3Vsignalsandareconnectedthroughleveltranslatorstotheon-boardscanchain.

TheJTAGsignalsattheFMCinterfaceusethe3.

3Vandarelevelshiftedupfrom1.

8Vintherestofthecard.

Page8FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5ClocksTheADM-VPX3-7V2providesawidevarietyofclockingoptions.

Fixedclocksat200MHzand250MHzaredistributedthroughouttheFPGA.

Additionally,theADM-VPX3-7V2provides4user-programmableclocks.

TheseclockscanbecombinedwiththeFPGA'sinternalPLLstosuitawidevarietyofcommunicationprotocols.

AcompleteoverviewoftheclockroutingontheADM-VPX3-7V2isgiveninFigureClocks.

Adescriptionofeachclockfollows.

Figure7:ClocksNote:ClockTerminationTheLVDSclocksdonothaveterminationresistorsonthecircuitboard.

On-dieterminationsintheFPGAmustbeenabledbysettingtheattribute"DIFF_TERM=TRUE".

Thiscaneitherbesetinthesourcecodewheninstantiatingthebuffer,orintheUserConstraintsFile(UCF).

SeetheXilinxVirtex-7LibrariesGuideandConstraintsGuideforfurtherdetails.

Note:SuperLogicRegion(SLR)WhilemostMGTclockscanbesharedtothetilenorthandsouthofthereceivingtile,2000TdevicesemploystackedsiliconinterconnecttechnologyandarelimitedbySLRs.

MGTclockscanonlybesharedwithinaSLRtothetilenorthorsouthoftheirreceivingtile.

SLRsareshownbydottedlinesinFigureClocks.

Page9FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5.

1200MHzReferenceClock(REFCLK200M)Thefixed200MHzreferenceclockREFCLK200MisadifferentialclocksignalusingLVDS.

REFCLK200MisconnectedtoaMRCCinputsontheTargetFPGAonBank14.

REFCLK200MisalsoconvertedtoHSTLsignalingandusedastheinputclockfortheDRAMinterface.

Thisclockcanbeusedtogenerateapplication-specificclockfrequenciesusingthePLLswithintheVirtex-7FPGA.

ItisalsosuitableasthereferenceclockfortheIOdelaycontrolblock(IDELAYCTRL).

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinREFCLK200M200MHzIO_L12_T2_MRCC_14LVDSAK34AL34REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_16HSTL_IAD32AD33REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_18HSTL_IU36T37REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_35HSTL_IE34E35REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_37HSTL_ID27D28Table4:REFCLK200MConnections3.

5.

2250MHzReferenceClock(REFCLK200M)Thefixed250MHzreferenceclockREFCLK250MisadifferentialclocksignalusingLVDS.

REFCLK250MisconnectedtoMGTREFCLKinputsontheTargetFPGA.

ThisclockisidealforPCIereferenceclockingandmanyothercommunicationstandards.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinREFCLK250M250MHzMGTREFCLK0_118LVDSE10E9REFCLK250M250MHzMGTREFCLK0_116LVDST8T7REFCLK250M250MHzMGTREFCLK0_114LVDSAD8AD7REFCLK250M250MHzMGTREFCLK1_113LVDSAK8AK7REFCLK250M250MHzMGTREFCLK1_111LVDSBA10BA9Table5:REFCLK250MConnectionsPage10FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5.

3ProgrammableClocks(LCLK,PROGCLK0-4)TherearetwoprogrammableclocksourcesthatareforwardedthroughouttheFPGA.

TheseclocksareprogrammablethroughtheAlphaDataADM-XRCGen3SDK.

LCLKisgeneratedintheBridgeFPGAbytheAlphaDataADB3driverandoffersalessaccuratefrequencyresolution,butwithawiderprogrammablefrequencyrange.

PROGCLK[4:0]isgeneratedbyadedicatedprogrammableclockgeneratorICandoffersextremelyhighfrequencyresolutions(1ppmincrements).

PROGCLK[4:0]isgeneratedbyasinglesourceandbufferedtoallMGTtilesatthesamefrequencyandphase.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinLCLK5-700MHzIO_L13_MRCC_14LVDSAJ32AK32PROGCLK05-312.

5MHzMGTREFCLK0_119LVDSA10A9PROGCLK15-312.

5MHzMGTREFCLK0_117LVDSK8K7PROGCLK25-312.

5MHzMGTREFCLK0_115LVDSY8Y7PROGCLK35-312.

5MHzMGTREFCLK0_113LVDSAH8AH7PROGCLK45-312.

5MHzMGTREFCLK0_111LVDSAW10AW9Table6:PROGCLKConnections3.

5.

4FMC-CarrierMGTClock(MGTCLK_M2C)Thereferenceclocks"GBTCLK0_M2C"and"GBTCLK1_M2C"aredifferentialclocksignalsusingLVDS.

TheclockisprovidedbyanFMCmodulethroughtheFMCinterface.

ItisconnectedatMGT112ontheTargetFPGAforapplicationspecificfrequencies/linerates.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinGBTCLK0_M2CVariableMGTREFCLK0_112LVDSAT8AT7GBTCLK1_M2CVariableMGTREFCLK1_112LVDSAU10AU9Table7:MGTCLK_M2CConnections3.

5.

5FMC-CarrierSignalClocks(GCLK_M2C)TheFMCinterfaceutilizesnumerousclockcapableandclockdedicatedconnectionsbetweentheFPGAandtheFMCmodule.

TheADM-VPX3-7V2connectsallpossibleclockpinsontheFMCinterfacetoclockcapabelIOontheFPGA.

PleaseseeAppendixClockPinsformoredetails.

3.

5.

625MHzSourceEarlyboardrevisionsusedaFoxoscillator,typeFXO-LC526R-25.

00,whichhastotalstability=±25ppm.

CurrentmodelsusetheSiLabs511FCA25M0000BA9,withhastotalstability=±30ppm.

Page11FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

6FlashMemoryA512MbFlashMemory(Intel/NumonyxPC28F512P30EF)isusedtostoreconfigurationbitstreamsfortheBridgeandTargetFPGAs.

TheflashmemorycannotbeaccessedbythetargetFPGA.

HostaccessisonlypossiblethroughtheFLCTL,FLPAGEandFLDATAregistersintheBridgeFPGA.

Theregionofmemorybetweenaddresses0x11000000and0x11FFFFFisallocatedforcustomdatatobestoredbytheADM-VPX3-7V2user.

Utilitiesforerasing,programmingandverificationoftheflashmemoryareprovidedintheADMXRCSDK.

WriteProtectTheFlashWriteProtect(WP#)pinisconnectedtoaninvertedversionoftheNVMROsignalattheXMCinterface.

WhentheNVMROsignalisactive(High),allwritestotheflashwillbeinhibited.

ThisstatewillbeindicatedbytheAmberLEDasshowninFigureLEDLocations.

Figure8:FlashMemoryMapPage12FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

7Configuration3.

7.

1Power-UpSequenceIfvaliddataisstoredintheflashmemory,thebridgewillautomaticallyconfiguretheTargetFPGAatpower-up.

ThissequencecanbeinhibitedbyturningtheFlashBootInhibit(FBI)switch.

(SeeTableSwitchDefinitions).

Note:Ifanover-temperaturealertisdetectedfromtheSystemMonitor,thetargetwillbeclearedbypulsingitsPROGsignal.

SeeSectionAutomaticTemperatureMonitoring.

3.

7.

2Bridge-LessModeWhenoperatinginbridgelessmode,theTargetFPGAwillbeconfigureddirectlybyaQuadSPIconnectiontoa512MbFLASHmemorydevice.

Thismemorydeviceisre-programableoveraXilinxJTAGcable.

Page13FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

8HealthMonitoringTheADM-VPX3-7V2hastheabilitytomonitortemperatureandvoltagetomaintainacheckontheoperationoftheboard.

ThemonitoringisimplementedusingtheATMEGA128microcontroller.

ControlalgorithmswithinthemicrocontrollerautomaticallychecklinevoltagesandonboardtemperaturesandsharestheinformationwithblockramintheBridgeFPGA.

Thefollowingvoltagerailsandtemperaturesaremonitored:MonitorPurpose1.

0VFPGACoreSupply(VccINT)1.

0VTargetTransceiverPower(AVCC)1.

2VTargetTransceiverPower(AVTT)1.

2VBridgeTransceiverPower(AVTT)1.

5VDDR3SDRAM,TargetFPGAmemoryI/OFMC_VADJ(Front-Panel)I/Ovoltage(1.

8Vorlower)1.

8VTargetTransceiverPower(AVCC_AUX)1.

8VFlashMemory,FPGAIOVoltage(VCCO)2.

0VTargetFPGAAuxiliarySupplyAUX(VccAUX)2.

5VLevelTranslation,BridgeFPGAAuxiliarySupply(VccAUX)3.

3VFromVPXP05.

0VFromVPXP012.

0VFromVPXP0Temp1TargetFPGAon-dietemperatureTemp2Boardtemperaturesensoron-dietemperatureTemp3BridgeFPGAon-dietemperatureTable8:VoltageandTemperatureMonitorsAnexampleapplicationthatreadsthesystemmonitor("sysmon")isavailablewithintheSDK.

Page14FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

8.

1AutomaticTemperatureMonitoringAtpower-up,thecontrollogicsetsthetemperaturelimitsandresetstheLM87'sover-temperatureinterrupt.

ThetemperaturelimitsareshowninTableTemperatureLimits:.

TargetFPGABridgeFPGABoardMinMaxMinMaxMinMaxCommercial0degC+85degC0degC+85degC0degC+85degCExtended0degC+100degC0degC+100degC0degC+100degCIndustrial-40degC+100degC-40degC+100degC-40degC+100degCTable9:TemperatureLimitsImportant:Ifanytemperaturelimitisexceeded,theTargetFPGAisautomaticallycleared.

ThisisindicatedbytheGreenLED(TargetConfigured)switchingoffandthetwostatusLEDsshowingatemperaturefaultindication.

Thepurposeofthismechanismistoprotectthecardfromdamageduetoover-temperature.

Itispossiblethatitwillcausetheuserapplicationand,possibly,thehostcomputerto"hang".

3.

8.

2MicrocontrollerStatusLEDsLEDsD7(Red)andD8(Green)indicatethemicrocontrollerstatus.

LEDsStatusGreenRunningandnoalarmsGreen+RedStandby(Poweredoff)FlashingGreen+FlashingRed(together)Attention-criticalalarmactiveFlashingGreen+FlashingRed(alternating)ServiceModeFlashingGreen+RedAttention-alarmactiveRedMissingapplicationfirmwareorinvalidfirmwareFlashingRedFPGAconfigurationclearedtoprotectboardTable10:StatusLEDDefinitionsPage15FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

9LocalBusAMultiplexedPacketTransportlink(MPTL)connectstheBridgeandTargetFPGAs.

Itiscapableoftransferringdataatupto2GB/ssimultaneouslyineachdirection.

TheMPTLreplacestheparallellocalbususedinpreviousgenerationsoftheADM-XRCseries.

DetailsofthelinkandexampledesignsaregivenintheSoftwareDevelopmentKit(SDK).

3.

10TargetFPGA3.

10.

1TargetFPGACharacteristicsTheADM-VPX3-7V2supportsVirtex-7V585T,V2000T,VX330T,VX485T,andVX690TdevicesintheFF(G),FH(G),andFLG(G)1761packages.

ThedistinguishingcharacteristicsofthesedevicesaredescribedinTableTargetFPGACharacteristics.

ThesefiguresaretakenfromtheVirtex-7FPGAFeatureSummaryavailableintheXilinx7seriesOverview.

ThemaximumuserI/OtotheVPXbackplanedoesnotchangewithdeviceselected.

HoweverFMCuserI/OisreducedsignificanlywithVX330TandVX485Tdevices.

DeviceLogicCellsSlicesDistributedRAMDSPSlicesBlockRAMCMTsPCIeHardMacrosXC7VX330T326,40051,0004,388Kb1,12027,000Kb142Gen3XC7VX485T485,76075,9008,175Kb2,80037,080Kb144Gen2XC7VX690T693,120108,30010,888Kb3,60052,920Kb203Gen3XC7V585T582,72091,0506,938Kb1,26028,620Kb183Gen2XC7V2000T1,954,560305,40021,550Kb2,16046,512Kb244Gen2Table11:TargetFPGACharacteristics3.

10.

2I/OBankVoltagesTheTargetFPGAIOisarrangedinbanks,eachwiththeirownsupplypins.

Thebanknumbers,theirvoltageandfunctionareshowninTableTargetFPGAIOBanks.

FulldetailsoftheIOSTANDARDrequiredforeachsignalaregivenintheSDK.

IOBanksVoltagePurpose0,141.

8VConfiguration,JTAG,LBusControl,TargetSelectMapInterface131.

8VRGMIIto1000Base-X391.

8VP2GPIO31,32,33FMC_VADJFMCInterface(variablevoltage,1.

8Vmax)12FMC_VIO_BFMCInterface(variablevoltage,1.

8VMax)15,16,18,19,34,35,37,381.

5VDRAMBanks0-3Table12:TargetFPGAIOBanksPage16FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

10.

3TargetMGTLinksThereareatotalof34Multi-GigabitTransceiver(MGT)linksconnectedtotheTargetFPGA:LinksWidthConnectionPCIe(3:0)4BridgeFPGA(forMPTL)orVPXP1Wafers1-4inBridgeBypassModePCIe(7:4)4DirectlinktoVPXP1Wafers5-8P1Expansion(3:0)4DirectlinktoVPXP1Wafer9-12UserDefined(11:0)12DirectlinktoVPXP2Wafer7-16andVPXP1Wafers13and14FMCMGT(9:0)10DirectlinktoFMCinterfaceTable13:TargetMGTLinksTheconnectionsoftheselinksareshowninFigureADM-VPX3-7V2BlockDiagram:ForMGTClockingseeFigureClocks:Page17FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

11MemoryInterfacesTheADM-VPX3-7V2hasfourindependentbanksofDDR3SDRAM.

Eachbankconsistsoftwo16bitwidememorydevicesinparalleltoprovidea32bitdatapathcapableofrunningupto800Hz(DDR-1600).

2Gbdevices(MicronMT41K128M16JT-125)arefittedasstandardtoprovide512MBperbank.

4Gb(giving1GBperbank)and8Gb(2GBperbank)areavailableasanorderingoption.

ThememorybanksarearrangedforcompatibilitywiththeXilinxMemoryInterfaceGenerator(MIG).

FigureDRAMBanksShowsthecomponentreferencesandFPGAbanksused.

Fulldetailsoftheinterface,signalingstandardsandanexampledesignareprovidedintheSDK.

Figure9:DRAMBanksSpeedGradeSingleRank(2GB-8GB)-31600-2/-2L/-2G1600-11600-1M1066Table14:MaximumMemorySpeedsPage18FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

12FMCInterfaceandFront-PanelI/OTheFMCinterfaceprovidesahigh-performanceandflexiblefront-panelinterfacethrougharangeofinterchangeable,industrystandardIOmoduleswhichconnectatreceptacleJ3.

TheFMCinterfaceadherestoVITA57.

1.

TheADM-VPX3-7V2utilizesallpossibleFMCconnectivity.

ThisincludesallGPIO,allMGTlinks,andallclockcapableIO.

FMCI2Csignal(SCLandSDAatC30andC31)areconnectedtothesystemmonitormicrocontroller.

Theyareusedtodetermineoperatingvoltageduringstartupandarenotaccesabletotheuser.

TheFMCPresentsignal(PRSNT_M2C_LatconnectorpinH2)isbufferedtoFPGApinAN33whichisa1.

8VcompatibleIOpin.

Note:TheADM-VPX3-7V2supportsonly1.

8VandlowerVADJVoltages.

Note:IfVX330TorVX485TFPGAsareselectedasthetarget,theFMCinterfacewilllosesignificantfunctionality.

Seepinassignmentsfordetails.

Page19FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016PageIntentionallyleftblankPage20FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixA:P1PinAssignmentsAppendixA.

1:DataPlane(P1Wafers1-4)SignalVPXP1FPGA|FPGAVPXP1SignalPCIE_TX0_PorLLINK_T2B0_PD1J2|H8A1PCIE_RX0_PorLLINK_B2T0_PPCIE_TX0_NorLLINK_T2B0_NE1J1|H7B1PCIE_RX0_NorLLINK_B2T0_NPCIE_TX1_PorLLINK_T2B1_PE2H4|G6B2PCIE_RX1_PorLLINK_B2T1_PPCIE_TX1_NorLLINK_T2B1_NF2H3|G5C2PCIE_RX1_NorLLINK_B2T1_NPCIE_TX2_PorLLINK_T2B2_PD3G2|F8A3PCIE_RX2_PorLLINK_B2T2_PPCIE_TX2_NorLLINK_T2B2_NE3G1|F7B3PCIE_RX2_NorLLINK_B2T2_NPCIE_TX3_PorLLINK_T2B3_PE4F4|E6B4PCIE_RX3_PorLLINK_B2T3_PPCIE_TX3_NorLLINK_T2B3_NF4F3|E5C4PCIE_RX3_NorLLINK_B2T3_NTable15:DataPlane(P1Wafers1-4)Note:ThisbusisonlyconnectedtothetargetFPGAwheninBridgeBypassmode.

OtherwisethisbusisconnectedtotheAlphaDataBridge.

SeeTableSwitchDefinitionsforBridgeBypassmodedetails.

AppendixA.

2:Data/ExpansionPlane(P1Wafers5-8)SignalVPXP1FPGA|FPGAVPXP1SignalPCIE_TX4_PD5K4|J6A5PCIE_RX4_PPCIE_TX4_NE5K3|J5B5PCIE_RX4_NPCIE_TX5_PE6L2|L6B6PCIE_RX5_PPCIE_TX5_NF6L1|L5C6PCIE_RX5_NPCIE_TX6_PD7M4|N6A7PCIE_RX6_PPCIE_TX6_NE7M3|N5B7PCIE_RX6_NPCIE_TX7_PE8N2|P8B8PCIE_RX7_PPCIE_TX7_NF8N1|P7C8PCIE_RX7_NTable16:Data/ExpansionPlane(P1Wafers5-8)Page21P1PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixA.

3:Expansion/UserPlane(P1Wafers9-14)SignalVPXP1FPGA|FPGAVPXP1SignalP1_TX0_PD9E2|D8A9P1_RX0_PP1_TX0_NE9E1|D7B9P1_RX0_NP1_TX1_PE10D4|C6B10P1_RX1_PP1_TX1_NF10D3|C5C10P1_RX1_NP1_TX2_PD11C2|B8A11P1_RX2_PP1_TX2_NE11C1|B7B11P1_RX2_NP1_TX3_PE12B4|A6B12P1_RX3_PP1_TX3_NF12B3|A5C12P1_RX3_NP1_TX4_PD13AH4|AE6A13P1_RX4_PP1_TX4_NE13AH3|AE5B13P1_RX4_NP1_TX5_PE14AG2|AD4B14P1_RX5_PP1_TX5_NF14AG1|AD3C14P1_RX5_NTable17:Expansion/UserPlane(P1Wafers9-14)AppendixA.

4:ControlPlane(P1Wafers15-16)SignalVPXP1Component.

Pin|Component.

PinVPXP1SignalETH2_TX_PD15U10.

4|U10.

1A15ETH2_RX_PETH2_TX_NE15U10.

5|U10.

2B15ETH2_RX_NETH1_TX_PE16U11.

4|U11.

1B16ETH1_RX_PETH1_TX_NF16U11.

5|U11.

2C16ETH1_RX_NTable18:ControlPlane(P1Wafers15-16)Thecontrolplane1000Base-XEthernetonWafer16iscontrolledbythetargetFPGAusinganRGMIIinterfacetoaMarvell88E1512.

SeepinassignmentbelowforRGMIIconnectivitydetails.

SignalFPGA|FPGASignalETH1_TXD0AW36|AT36ETH1_RXD0ETH1_TXD1AV36|AT34ETH1_RXD1ETH1_TXD2AY34|AU34ETH1_RXD2ETH1_TXD3BA35|AU36ETH1_RXD3ETH1_TX_CTRLBA34|AT32ETH1_RX_CTRLETH1_TX_CLKAW32|AV34ETH1_RX_CLKETH1_MDCAU32|AV33ETH1_MDIOETH1_CLK125AY32|--Table19:RGMIIto1000Base-XPHYPage22P1PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixB:P2PinAssignmentsAppendixB.

1:GPIO24s/12d+8s(P2Wafers1-6)SignalVPXP2FPGA|FPGAVPXP2SignalGP1_PE6C16|B16F6GP1_NGP2_PB6C15|C14C6GP2_NGP3_PD5B14|A14E5GP3_NGP4_PA5D16|D15B5GP4_NGP5_PE4D13|C13F4GP5_NGP6_PB4E12|D12C4GP6_NGP7_PD3F16|E15E3GP7_NGP8_PA3G12|F12B3GP8_NGP9_PE2E14|E13F2GP9_NGP10_PB2J13|H13C2GP10_NGP11_PD1F15|F14E1GP11_NGP12_PA1H16|G16B1GP12_NGP13G1M13|N14G3GP14GP15G5N13|N15G7GP16GP17G9N16|M12G11GP18GP19G13M11|M16G15GP20Table20:GPIO24s/12d+8s(P2Wafers1-6)Allsingleendedpinscanfunctionaspush-pullupto60MbpsorOpen-drainupto2Mbps.

DifferentialoperationislimitedonlybyFPGAIOpins.

SwitchingbetweenSingleEndedanddifferentialsignalingisdescribedinTableSwitchDefinitions.

Page23P2PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixB.

2:MGTLanes20d(P2Wafers7-16)SignalVPXP2FPGA|FPGAVPXP2SignalP2_TX0_PD7U2|W6A7P2_RX0_PP2_TX0_NE7U1|W5B7P2_RX0_NP2_TX1_PE8T4|V4B8P2_RX1_PP2_TX1_NF8T3|V3C8P2_RX1_NP2_TX2_PD9R2|U6A9P2_RX2_PP2_TX2_NE9R1|U5B9P2_RX2_NP2_TX3_PE10P4|R6B10P2_RX3_PP2_TX3_NF10P3|R5C10P2_RX3_NP2_TX4_PD11AE2|AC6A11P2_RX4_PP2_TX4_NE11AE1|AC5B11P2_RX4_NP2_TX5_PE12AC2|AB4B12P2_RX5_PP2_TX5_NF12AC1|AB3C12P2_RX5_NP2_TX6_PD13AA2|AA6A13P2_RX6_PP2_TX6_NE13AA1|AA5B13P2_RX6_NP2_TX7_PE14W2|Y4B14P2_RX7_PP2_TX7_NF14W1|Y3C14P2_RX7_NP2_TX8_PD15AK4|AG6A15P2_RX8_PP2_TX8_NE15AK3|AG5B15P2_RX8_NP2_TX9_PE16AJ2|AF4B16P2_RX9_PP2_TX9_NF16AJ1|AF3C16P2_RX9_NTable21:MGTLanes20d(P2Wafers7-16)Page24P2PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixC:FMCPinAssignmentsAppendixC.

1:GPIOPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalLA00_CC_PG6AU23|AV23G7LA00_CC_NLA01_CC_PD8AT22|AU22D9LA01_CC_NLA02_PH7AM24|AN24H8LA02_NLA03_PG9AJ23|AK23G10LA03_NLA04_PH10AK20|AL20H11LA04_NLA05_PD11AL21|AM21D12LA05_NLA06_PC10AJ21|AJ20C11LA06_NLA07_PH13AR24|AT24H14LA07_NLA08_PG12AM23|AN23G13LA08_NLA09_PD14AP23|AP22D15LA09_NLA10_PC14AN21|AP21C15LA10_NLA11_PH16BA22|BB22H17LA11_NLA12_PG15AT21|AU21G16LA12_NLA13_PD17AV21|AW21D18LA13_NLA14_PC18BA21|BB21C19LA14_NLA15_PH19AY24|BA24H20LA15_NLA16_PG18BB24|BB23G19LA16_NLA17_CC_PD20AW23|AW22D21LA17_CC_NLA18_CC_PC22AR23|AR22C23LA18_CC_NLA19_PH22AU24|AV24H23LA19_NLA20_PG21AY25|BA25G22LA20_NLA21_PH25AJ22|AK22H26LA21_NLA22_P*G24AU19|AV19G25LA22_N*LA23_P*D23AR18|AR17D24LA23_N*LA24_P*H28AN19|AN18H29LA24_N*LA25_P*G27AP20|AR19G28LA25_N*LA26_P*D26AV16|AW16D27LA26_N*LA27_P*C26AT20|AT19C27LA27_N*LA28_P*H31AK19|AK18H32LA28_N*LA29_P*G30AL19|AM19G31LA29_N*LA30_P*H34AK17|AL17H35LA30_N*Table22:GPIOPins(continuedonnextpage)Page25FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SignalFMC(J1)FPGA|FPGAFMC(J1)SignalLA31_P*G33AM18|AM17G34LA31_N*LA32_P*H37AP18|AP17H38LA32_N*LA33_P*G36AM16|AN16G37LA33_N*HA00_CC_P*F4AV13|AW13F5HA00_CC_N*HA01_CC_P*E2AU14|AU13E3HA01_CC_N*HA02_P*K7AJ16|AJ15K8HA02_N*HA03_P*J6AJ13|AJ12J7HA03_N*HA04_P*F7AK14|AK13F8HA04_N*HA05_P*E6AK15|AL14E7HA05_N*HA06_P*K10AL16|AL15K11HA06_N*HA07_P*J9AM12|AM11J10HA07_N*HA08_P*F10AN11|AP11F11HA08_N*HA09_P*E9AM13|AN13E10HA09_N*HA10_P*K13AN15|AN14K14HA10_N*HA11_P*J12AP12|AR12J13HA11_N*HA12_P*F13AY14|AY13F14HA12_N*HA13_P*E12AW12|AY12E13HA13_N*HA14_P*J15BB14|BB13J16HA14_N*HA15_P*F16BA15|BA14F17HA15_N*HA16_P*E15AV15|AV14E16HA16_N*HA17_CC_P*K16AP13|AR13K17HA17_CC_N*HA18_P*J18BA16|BB16J19HA18_N*HA19_P*F19AR15|AT15F20HA19_N*HA20_P*E18AR14|AT14E19HA20_N*HA21_P*K19AT12|AU12K20HA21_N*HA22_P*J21AY19|BA19J22HA22_N*HA23_P*K22AY20|BA20K23HA23_N*HB00_CC_P*K25AR27|AT27K26HB00CC__N*HB01_P*J24BA26|BA27J25HB01_N*HB02_P*F22AV25|AV26F23HB02_N*HB03_P*E21BB26|BB27E22HB03_N*HB04_P*F25AY27|AY28F26HB04_N*HB05_P*E24BB28|BB29E25HB05_N*HB06_CC_P*K28AU26|AU27K29HB06_CC_N*HB07_P*J27AW27|AW28J28HB07_N*HB08_P*F28AU29|AV29F29HB08_N*Table22:GPIOPins(continuedonnextpage)Page26FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SignalFMC(J1)FPGA|FPGAFMC(J1)SignalHB09_P*E27AW25|AW26E28HB09_N*HB10_P*K31AR29|AT29K32HB10_N*HB11_P*J30AU28|AV28J31HB11_N*HB12_P*F31AN28|AP28F32HB12_N*HB13_P*E30AT25|AT26E31HB13_N*HB14_P*K34AL25|AL26K35HB14_N*HB15_P*J33AM26|AM27J34HB15_N*HB16_P*F34AK27|AL27F35HB16_N*HB17_CC_P*K37AP27|AR28K38HB17_CC_N*HB18_P*J36AK24|AK25J37HB18_N*HB19_P*E33AP25|AR25E34HB19_N*HB20_P*F37AN25|AN26F38HB20_N*HB21_P*E36AJ25|AJ26E37HB21_N*FMC_CLK_DIR_1V8*B1BB12|---Table22:GPIOPinsAppendixC.

2:ClockPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalGBTCLK0_M2C_P*D4AT8|AT7D5GBTCLK0_M2C_N*GBTCLK1_M2C_P*B20AU10|AU9B21GBTCLK1_M2C_N*CLK0_M2C_P*H4AY18|AY17H5CLK0_M2C_N*CLK1_M2C_P*G2AT17|AU17G3CLK1_M2C_N*CLK2_BIDIR_P*K4AU18|AV18K5CLK2_BIDIR_N*CLK3_BIDIR_P*J2AW18|AW17J3CLK3_BIDIR_N*Table23:ClockPins*ForXCVX330TorXCVX485TpinsnotconnectedPage27FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixC.

3:MGTPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalDP0_M2C_PC6AN6|AP4C2DP0_C2M_PDP0_M2C_NC7AN5|AP3C3DP0_C2M_NDP1_M2C_PA2AM8|AN2A22DP1_C2M_PDP1_M2C_NA3AM7|AN1A23DP1_C2M_NDP2_M2C_PA6AL6|AM4A26DP2_C2M_PDP2_M2C_NA7AL5|AM3A27DP2_C2M_NDP3_M2C_PA10AJ6|AL2A30DP3_C2M_PDP3_M2C_NA11AJ5|AL1A31DP3_C2M_NDP4_M2C_P*A14AV8|AV4A34DP4_C2M_P*DP4_M2C_N*A15AV7|AV3A35DP4_C2M_N*DP5_M2C_P*A18AU6|AU2A38DP5_C2M_P*DP5_M2C_N*A19AU5|AU1A39DP5_C2M_N*DP6_M2C_P*B16AR6|AT4B36DP6_C2M_P*DP6_M2C_N*B17AR5|AT3B37DP6_C2M_N*DP7_M2C_P*B12AP8|AR2B32DP7_C2M_P*DP7_M2C_N*B13AP7|AR1B33DP7_C2M_N*DP8_M2C_P*B8BB8|BB4B28DP8_C2M_P*DP8_M2C_N*B9BB7|BB3B29DP8_C2M_N*DP9_M2C_P*B4BA6|BA2B24DP9_C2M_P*DP9_M2C_N*B5BA5|BA1B25DP9_C2M_N*Table24:MGTPins*ForXCVX330TorXCVX485TpinsnotconnectedPage28FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016RevisionHistoryDateRevisionChangedByNatureofChange10Oct20120.

1K.

RothInitialDraft14Mar20131.

0K.

RothInitialRelease,finalizedappendix29Oct20131.

1K.

RothUpdatedFigureClocksto25MHzonboardoscilator,TablePROGCLKConnectionsfixedtoshowPROGCLK[4:0]insteadof[3:0],UpdatedmiscellaneousAppendixtablecolumnheaderstoshowVPXP1whereappropriate.

14Nov20131.

2K.

RothUpdatedSectionAUXCLKtoshowpinassignments.

19Nov20131.

3K.

RothUpdatedFigureADM-VPX3-7V2BlockDiagramandTableRGMIIto1000Base-XPHY.

23Jan20141.

4K.

RothAddedSectionVPXP2GPIO6Feb20141.

5K.

RothCorrectedPROGCLK0andPROGCLK1inClocks18Feb20141.

6K.

RothChangedSystemRequirementstospecify5.

0VasthedefaultVPWRoption.

8Jul20141.

7K.

RothAddedAutomaticTemperatureMonitoringandMaximumMemorySpeeds16Oct20151.

8K.

RothUpdatedJTAGInterfacetocorrectJ3referencedesignation,FMCInterfaceandFront-PanelI/OtoincludeFMCPresentandI2Cdescription,andadded25MHzSource.

22Aug20161.

9K.

RothUpdatedMemoryInterfacestoremovedualrank8Gboptionasmicronhasmovedthisparttosinglerank.

Page29FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016PageIntentionallyleftblankAddress:4WestSilvermillsLane,Edinburgh,EH35BD,UKTelephone:+441315582600Fax:+441315582700email:sales@alpha-data.

comwebsite:http://www.

alpha-data.

comAddress:3507RingsbyCourtSuite105,Denver,CO80216Telephone:(303)9548768Fax:(866)8209956tollfreeemail:sales@alpha-data.

comwebsite:http://www.

alpha-data.

com4.

5

922ndAugust2016ADM-VPX3-7V2UserManualV1.

9-22ndAugust20162016CopyrightAlphaDataParallelSystemsLtd.

Allrightsreserved.

ThispublicationisprotectedbyCopyrightLaw,withallrightsreserved.

Nopartofthispublicationmaybereproduced,inanyshapeorform,withoutpriorwrittenconsentfromAlphaDataParallelSystemsLtd.

HeadOfficeAddress:4WestSilvermillsLane,Edinburgh,EH35BD,UKTelephone:+441315582600Fax:+441315582700email:sales@alpha-data.

comwebsite:http://www.

alpha-data.

comUSOffice3507RingsbyCourtSuite105,Denver,CO80216(303)9548768(866)8209956tollfreesales@alpha-data.

comhttp://www.

alpha-data.

comAlltrademarksarethepropertyoftheirrespectiveowners.

ADM-VPX3-7V2UserManualV1.

9-22ndAugust2016TableOfContents1Introduction11.

1KeyFeatures11.

2References&Specifications22Installation32.

1SoftwareInstallation32.

2HardwareInstallation32.

2.

1SystemRequirements32.

2.

2CoolingRequirements33FunctionalDescription43.

1Overview43.

1.

1SwitchDefinitions53.

1.

2LEDDefinitions63.

2VPXP0Interface73.

2.

1MVMRO73.

2.

2SYSRESET#73.

2.

3AUXCLK73.

2.

4REFCLK73.

3VPXP2GPIO73.

3.

1LVDS73.

3.

2CMOS73.

4JTAGInterface83.

4.

1On-boardInterface83.

4.

2VPXInterface83.

4.

3JTAGVoltages83.

5Clocks93.

5.

1200MHzReferenceClock(REFCLK200M)103.

5.

2250MHzReferenceClock(REFCLK200M)103.

5.

3ProgrammableClocks(LCLK,PROGCLK0-4)113.

5.

4FMC-CarrierMGTClock(MGTCLK_M2C)113.

5.

5FMC-CarrierSignalClocks(GCLK_M2C)113.

5.

625MHzSource113.

6FlashMemory123.

7Configuration133.

7.

1Power-UpSequence133.

7.

2Bridge-LessMode133.

8HealthMonitoring143.

8.

1AutomaticTemperatureMonitoring153.

8.

2MicrocontrollerStatusLEDs153.

9LocalBus163.

10TargetFPGA163.

10.

1TargetFPGACharacteristics163.

10.

2I/OBankVoltages163.

10.

3TargetMGTLinks173.

11MemoryInterfaces183.

12FMCInterfaceandFront-PanelI/O19AppendixAP1PinAssignments21A.

1DataPlane(P1Wafers1-4)21A.

2Data/ExpansionPlane(P1Wafers5-8)21A.

3Expansion/UserPlane(P1Wafers9-14)22A.

4ControlPlane(P1Wafers15-16)22ADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixBP2PinAssignments23B.

1GPIO24s/12d+8s(P2Wafers1-6)23B.

2MGTLanes20d(P2Wafers7-16)24AppendixCFMCPinAssignments25C.

1GPIOPins25C.

2ClockPins27C.

3MGTPins28ListofTablesTable1References2Table2SwitchDefinitions5Table3LEDDefinitions6Table4REFCLK200MConnections10Table5REFCLK250MConnections10Table6PROGCLKConnections11Table7MGTCLK_M2CConnections11Table8VoltageandTemperatureMonitors14Table9TemperatureLimits15Table10StatusLEDDefinitions15Table11TargetFPGACharacteristics16Table12TargetFPGAIOBanks16Table13TargetMGTLinks17Table14MaximumMemorySpeeds18Table15DataPlane(P1Wafers1-4)21Table16Data/ExpansionPlane(P1Wafers5-8)21Table17Expansion/UserPlane(P1Wafers9-14)22Table18ControlPlane(P1Wafers15-16)22Table19RGMIIto1000Base-XPHY22Table20GPIO24s/12d+8s(P2Wafers1-6)23Table21MGTLanes20d(P2Wafers7-16)24Table22GPIOPins25Table23ClockPins27Table24MGTPins28ListofFiguresFigure1ADM-VPX3-7V2ProductPicture1Figure2ADM-VPX3-7V2AirCooled3Figure3ADM-VPX3-7V2BlockDiagram4Figure4LEDLocations6Figure5JTAGHeaderJ38Figure6JTAGBoundaryScanChain8Figure7Clocks9Figure8FlashMemoryMap12Figure9DRAMBanks18ADM-VPX3-7V2UserManualV1.

9-22ndAugust20161IntroductionTheADM-VPX3-7V2isahigh-performanceXMCforapplicationsusingVirtex-7FPGAsfromXilinx.

ThiscardsupportsVirtex-7devicesavailableintheFF(G),FH(G),andFL(G),1761package.

TheADM-VPX3-7V2includesaseparateFPGAwithaPCIebridgedevelopedbyAlphaData.

Usingaseparatedeviceallowshighperformanceoperationwithouttheneedtointegrateproprietarycoresintheuser(target)FPGA.

Withthereleaseof7seriesFPGAboards,AlphaDatahasintroducedanewbuildoptiontoallowthemezzaninecardtobeassembledwithoutthebridgetoreducepowerandcost.

TheADM-VPX3-7V2isavailableinair-cooledandconduction-cooledconfigurations(with2LevelMaintenancecompatibility).

ViewtheADM-VPX3-7V2OrderingInfotabatADM-VPX3-7V2ProductPageonwww.

alpha-data.

com.

Figure1:ADM-VPX3-7V2ProductPicture1.

1KeyFeaturesKeyFeaturesOpenVPXComplianceList3UOpenVPX,complianttoVITAStandard46.

0and65Dedicated4-lanePCI-ExpressGen2interfacewithhigh-performanceDMAcontrollers4additionalPCI-ExpresscompliantGTXlinksbetweenuserFPGAandOpenVPXDataPlane4laneExpansionportcomplianttoOpenVPX2Controlplaneconnections,onetouserFPGA,onetoBridgeP2ConnectorcomplianttoVita46.

9X24S+X8D+X12DSupportforVirtex-7FPGAinFF(G),FH(G),andFLG(G)1761package4independentbanksofDDR3-1600SDRAM,512MB/bank,2GBtotal(4GBoption)FMCfrontpanelinterfacecompliantwithVita57.

1utilizingallIOandallHigh-Speedlinks.

1PPSCapableviaOpenVPXAUXCLKClocksynchronizationwithOpenVPXREFCLKOn-boardprogrammableclocksenablingmultipleprotocolstobeimplementedontheuserFPGA'shigh-speedlinksVoltageandtemperaturemonitoringAir-cooled,conduction-cooled,and2LevelMaintenanceconfigurationsavailableSLT3-PAY-2F1F2U-14.

2.

1Page1Introductionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SLT3-PAY-1F2F2U-14.

2.

2SLT3-PAY-2F2U-14.

2.

3SLT3-PAY-1F1F2U-14.

2.

4SLT3-PAY-1D-14.

2.

6SLT3-PAY-2F-14.

2.

7SLT3-PAY-1F4U-14.

2.

8SLT3-PAY-8U-14.

2.

9SLT3-PER-2F-14.

3.

1SLT3-PER-1F-14.

3.

2SLT3-PER-1U-14.

3.

31.

2References&SpecificationsANSI/VITA46.

0VPXBaselineStandard,October2007,VITA,ISBN1-885731-44-2ANSI/VITA46.

9PMC/MXCRearI/OFabricSignalMappingon3Uand6UVPXModulesStandard,November2010,VITA,ISBN1-885731-63-9ANSI/VITA48.

2MechanicalSpecificationsforMicrocomputersUsingREDIConductionCoolingAppliedtoVITAVPX,July2010,VITA,ISBN1-885731-60-4ANSI/VITA57.

1FPGAMezzanineCard(FMC)Standard,February2010,VITA,ISBN1-885731-49-3ANSI/VITA65OpenVPXSystemSpecification,June2010,VITA,ISBN1-885731-58-2Table1:ReferencesPage2Introductionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20162Installation2.

1SoftwareInstallationPleaserefertotheSoftwareDevelopmentKit(SDK)installationCD.

TheSDKcontainsdrivers,examplesforhostcontrolandFPGAdesignwithcomprehensivehelponapplicationinterfacing.

2.

2HardwareInstallation2.

2.

1SystemRequirementsTheADM-VPX3-7V2isa3UOpenVPXcompliantFPGAcardwithFMCfrontIOinterface.

TousetheAlphaData'spowerfulAPIanddrivers,thesystemcontrollermustbecapableofdrivingthePCIelanestotheBridge.

TheADM-VPX3-7V2alsoutilizestheOpenVPX1000Base-Xcontrollines,thoughthisimplementationislefttotheuser.

P2complieswithVita46.

9X24S+X8D+X12Duserdefinedpinconfigurationwithanadditional8connectionstoP2RowG.

TheX24scanbeconfiguredaseither24songleendedsignalsat3.

3Vor12LVDSpairs(butnotboth).

TheeightuserdefinedsingleendedconnectionsinrowGare3.

3Vcompliantandcanbeisolatedfromthebackplaneviaonboardswitches.

AlphaDataoffersaRearTransitionModule(RTM)thatbreaksoutallP2IOandP1controllanesforuseinlabanddevelopmentenvironments(Partnumber:ADM-VPX3-7V2-RTM).

TheADM-VPX3-7V2canbeconfiguredtoeitherutilize5Vor12Vasthemainpowersource.

Thedefaultbuilduses5V,contactsales@alpha-data.

comfordetailsonthe12Vbuildoption.

2.

2.

2CoolingRequirementsThepowerdissipationoftheboardishighlydependentontheTargetFPGAapplication.

ApowerestimatorspreadsheetisavailableonrequestfromAlphaData.

ThisshouldbeusedinconjunctionwithXilinxpowerestimationtoolstodeterminetheapproximatecurrentrequirementsforeachpowerrail.

Theboardissuppliedwithapassiveaircooledorconductioncooledheatsinkaccordingtotheordernumbergivenattimeofpurchase.

Itistheusersresponsibilitytoensuresufficientairflowforaircooledapplicationsandappropriatemetalworkforconductioncooledapplications.

TheboardfeaturessystemmonitoringthatmeasurestheboardandFPGAtemperature.

Italsoincludesaself-protectionmechanismthatwillclearthetargetFPGAconfigurationifanover-temperatureconditionisdetected.

SeeSectionHealthMonitoringforhealthmonitoringdetails.

Figure2:ADM-VPX3-7V2AirCooledPage3Installationad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163FunctionalDescription3.

1OverviewFigure3:ADM-VPX3-7V2BlockDiagramPage4FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

1.

1SwitchDefinitionsThereisasetofeightDIPswitchesplacedonthebottomoftheboard.

TheirfunctionsaredescribedinTableSwitchDefinitions.

Note:AllswitchesareOFFbydefault.

FactoryConfigurationswitchmustbeintheOFFpositionfornormaloperation.

SwitchRef.

FunctionONStateOffStateSW1-1P2LVDS24sonP2useCMOS24sonP2useLVDSSW1-2InternalOscillatorUseVPXREFCLKUseInternalOscillatorsourceSW1-3BridgeBypassBridgeFPGAisbypassed-PCIelanes(3:0)areconnecteddirectlytotheuserFPGA.

BridgeFPGAisused.

PCIelanes(3:0)areconnectedtothebridge.

SW1-4FlashBootInhibitTargetFPGAisnotconfiguredfromonboardflashmemory.

TargetFPGAisconfiguredfromon-boardflashmemory.

SW1-5VPXJTAGConnectJTAGchaintoP0IsolateJTAGchainfromP0SW1-6E-FuseEnableE-Fuseprogrammingvoltage(VccEFuse=2.

5V)DisableE-Fuseprogrammingvoltage(VccEFuse=0V)SW1-7FactoryConfiguration-NormalOperationSW1-8Bridge-LessModeBridge-LessModeActive-UserbitstreamloadedfromSPIflashPCIeBridgeModeActive-UserbitstreamloadedfromBridgeTable2:SwitchDefinitionsPage5FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

1.

2LEDDefinitionsThepositionanddescriptionoftheboardstatusLEDsareshowninFigureLEDLocations:Figure4:LEDLocationsComp.

Ref.

FunctionONStateOffStateD11(Amber)MVMROInhibitwritestonon-volatilememoriesEnablewritestonon-volatilememoriesD12(Green)Status0SeesectionMicrocontrollerStatusLEDsERRORD13(Red)Status1SeesectionMicrocontrollerStatusLEDsERRORD14(Green)BridgeDoneBridgeFPGAisconfiguredBridgeFPGAisunconfiguredD15(Green)TargetDoneTargetFPGAisconfiguredTargetFPGAisunconfiguredD16(Amber)XMCJTAGJTAGchainconnectedtoP0JTAGchainisisolatedfromP0D17(Amber)BridgeBypassBridgeFPGAisbypassed-PCIelanes(3:0)directtouserFPGABridgeFPGAisused.

PCIelanes(3:0)areconnectedtothebridge.

D18(Amber)Bridge-LessTargetisconfiguredbySPImemoryTargetisconfiguredbyBridgeD5(Green)ETH1LED[0]LinkNoLinkD6(Green)ETH2LED[2]LinkNoLinkD7(Amber)ETH1LED[1]ReceiveNoReceiveD8(Amber)ETH2LED[1]ReceiveNoReceiveD9(Green)ETH1LED[2]LinkNoLinkD10(Green)ETH2LED[0]LinkNoLinkTable3:LEDDefinitionsPage6FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

2VPXP0Interface3.

2.

1MVMRONon-VolatileMemoryReadOnly.

Thissignalisaninputfromthesystem.

Whenasserted(high),allwritestonon-volatilememoriesareinhibited.

ThisisindicatedbytheAmberLED,D7.

Thissignalcannotbeinternallydrivenorover-ridden.

AbufferedversionofthesignalisconnectedtothetargetFPGA.

3.

2.

2SYSRESET#XMCResetIn.

Thissignalisanactivelowinputfromthesystem.

Whenasserted,thebridgeFPGAwillbereset.

ThisalsoactsandPCIReset.

TheSYSRESET#signalistranslatedto1.

8VlevelsandconnectedtothetargetFPGAatpinAF30.

3.

2.

3AUXCLKAuxiliaryClock.

ThisclockisadirectinputtothetargetFPGA.

InOpenVPXthisclocklineisusedfor1PPSsynchronizationsignaling.

AUXCLKislimitedto1.

8VbyaquickswitchandthepreferedsignalingstandardisLVDS.

AUXCLK_PisconnectedtoTargetFPGAMRCCpinG14AUXCLK_NisconnectedtoTargetFPGAMRCCpinG133.

2.

4REFCLKReferenceClock.

Thisclockisaninputtotheonboardclockdistributionandgenerationsystem.

The50MHzdefinedinOpenVPXcanbeusedtoalignallsystemclocks.

Alternativelyanonboard50MHzreferencecanbegeneratedasshowninTableSwitchDefinitions.

3.

3VPXP2GPIO3.

3.

1LVDSWhenSW1-1isOFF,theGPIOonP2iscompatiblewith1.

8VsignalingsuchasLVDSand1.

8Vsingleendedsignals.

Thesesignalsarerouteddifferentiallyasshowninthepinouttablesintheappendix.

TheFPGAisprotectedfrominappropriatesignallevelsbyanNXP74CBTLVD3861whichisalowresistancequickswitchthatclampsat1.

8Vineitherdirection,butcanacceptupto3.

3Vonaninput.

3.

3.

2CMOSWhenSW1-1isON,theGPIOonP2iscompatiblewith3.

3VsignalingsuchasTTLandCMOS.

ThesignalsarepassedthroughaTITXS0108ERGYRopen-drain,push-pull,compatibleautodirectionsensingleveltranslator.

ThisprotectstheFPGAfromhighervoltagesonthebackplanewhileallowingittocommunicateat3.

3Vlevels,compliantwithCMOSandTTLvoltages.

Theleveltranslatorhasapropagationdelayof5.

7nsmaxandachannel-to-channelskew(withinapackage)of1ns.

Therefore,itisonlysuitableforratesupto~50Mb/sPage7FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

4JTAGInterface3.

4.

1On-boardInterfaceAJTAGboundaryscanchainisconnectedtoheaderJ3.

ThisallowstheconnectionoftheXilinxJTAGcableforFPGAdebugusingtheXilinxChipScopetools.

TheJTAGHeaderpinoutisshowninFigureJTAGHeaderJ3:Figure5:JTAGHeaderJ3ThescanchainisshowninFigureJTAGBoundaryScanChain:Figure6:JTAGBoundaryScanChainIftheboundaryscanchainisconnectedtotheinterfaceattheVPXbackplane(SW1-5isON),headerJ3shouldnotbeused.

3.

4.

2VPXInterfaceTheJTAGinterfaceontheVPXbackplaneisnormallyunused.

WhenSW1-5isOFF(default),allJTAGsignalstoP0areleftfloating.

TheJTAGinterfacecanbeconnectedtotheVPXBackplane(throughlevel-translators)byswitchingSW1-5ON.

SeeTableSwitchDefinitions3.

4.

3JTAGVoltagesTheon-boardJTAGscanchainuses1.

8V.

TheVccsupplyprovidedonJ3totheJTAGcableis+1.

8Vandisprotectedbyapolyfuseratedat350mA.

3.

3VsignalsmustnotbeusedatheaderJ3.

TheJTAGsignalsattheXMCinterfaceuse3.

3Vsignalsandareconnectedthroughleveltranslatorstotheon-boardscanchain.

TheJTAGsignalsattheFMCinterfaceusethe3.

3Vandarelevelshiftedupfrom1.

8Vintherestofthecard.

Page8FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5ClocksTheADM-VPX3-7V2providesawidevarietyofclockingoptions.

Fixedclocksat200MHzand250MHzaredistributedthroughouttheFPGA.

Additionally,theADM-VPX3-7V2provides4user-programmableclocks.

TheseclockscanbecombinedwiththeFPGA'sinternalPLLstosuitawidevarietyofcommunicationprotocols.

AcompleteoverviewoftheclockroutingontheADM-VPX3-7V2isgiveninFigureClocks.

Adescriptionofeachclockfollows.

Figure7:ClocksNote:ClockTerminationTheLVDSclocksdonothaveterminationresistorsonthecircuitboard.

On-dieterminationsintheFPGAmustbeenabledbysettingtheattribute"DIFF_TERM=TRUE".

Thiscaneitherbesetinthesourcecodewheninstantiatingthebuffer,orintheUserConstraintsFile(UCF).

SeetheXilinxVirtex-7LibrariesGuideandConstraintsGuideforfurtherdetails.

Note:SuperLogicRegion(SLR)WhilemostMGTclockscanbesharedtothetilenorthandsouthofthereceivingtile,2000TdevicesemploystackedsiliconinterconnecttechnologyandarelimitedbySLRs.

MGTclockscanonlybesharedwithinaSLRtothetilenorthorsouthoftheirreceivingtile.

SLRsareshownbydottedlinesinFigureClocks.

Page9FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5.

1200MHzReferenceClock(REFCLK200M)Thefixed200MHzreferenceclockREFCLK200MisadifferentialclocksignalusingLVDS.

REFCLK200MisconnectedtoaMRCCinputsontheTargetFPGAonBank14.

REFCLK200MisalsoconvertedtoHSTLsignalingandusedastheinputclockfortheDRAMinterface.

Thisclockcanbeusedtogenerateapplication-specificclockfrequenciesusingthePLLswithintheVirtex-7FPGA.

ItisalsosuitableasthereferenceclockfortheIOdelaycontrolblock(IDELAYCTRL).

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinREFCLK200M200MHzIO_L12_T2_MRCC_14LVDSAK34AL34REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_16HSTL_IAD32AD33REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_18HSTL_IU36T37REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_35HSTL_IE34E35REFCLK200M_HSTL200MHzIO_L13_T1_MRCC_37HSTL_ID27D28Table4:REFCLK200MConnections3.

5.

2250MHzReferenceClock(REFCLK200M)Thefixed250MHzreferenceclockREFCLK250MisadifferentialclocksignalusingLVDS.

REFCLK250MisconnectedtoMGTREFCLKinputsontheTargetFPGA.

ThisclockisidealforPCIereferenceclockingandmanyothercommunicationstandards.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinREFCLK250M250MHzMGTREFCLK0_118LVDSE10E9REFCLK250M250MHzMGTREFCLK0_116LVDST8T7REFCLK250M250MHzMGTREFCLK0_114LVDSAD8AD7REFCLK250M250MHzMGTREFCLK1_113LVDSAK8AK7REFCLK250M250MHzMGTREFCLK1_111LVDSBA10BA9Table5:REFCLK250MConnectionsPage10FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

5.

3ProgrammableClocks(LCLK,PROGCLK0-4)TherearetwoprogrammableclocksourcesthatareforwardedthroughouttheFPGA.

TheseclocksareprogrammablethroughtheAlphaDataADM-XRCGen3SDK.

LCLKisgeneratedintheBridgeFPGAbytheAlphaDataADB3driverandoffersalessaccuratefrequencyresolution,butwithawiderprogrammablefrequencyrange.

PROGCLK[4:0]isgeneratedbyadedicatedprogrammableclockgeneratorICandoffersextremelyhighfrequencyresolutions(1ppmincrements).

PROGCLK[4:0]isgeneratedbyasinglesourceandbufferedtoallMGTtilesatthesamefrequencyandphase.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinLCLK5-700MHzIO_L13_MRCC_14LVDSAJ32AK32PROGCLK05-312.

5MHzMGTREFCLK0_119LVDSA10A9PROGCLK15-312.

5MHzMGTREFCLK0_117LVDSK8K7PROGCLK25-312.

5MHzMGTREFCLK0_115LVDSY8Y7PROGCLK35-312.

5MHzMGTREFCLK0_113LVDSAH8AH7PROGCLK45-312.

5MHzMGTREFCLK0_111LVDSAW10AW9Table6:PROGCLKConnections3.

5.

4FMC-CarrierMGTClock(MGTCLK_M2C)Thereferenceclocks"GBTCLK0_M2C"and"GBTCLK1_M2C"aredifferentialclocksignalsusingLVDS.

TheclockisprovidedbyanFMCmodulethroughtheFMCinterface.

ItisconnectedatMGT112ontheTargetFPGAforapplicationspecificfrequencies/linerates.

SignalFrequencyTargetFPGAInputIOStandard"P"pin"N"pinGBTCLK0_M2CVariableMGTREFCLK0_112LVDSAT8AT7GBTCLK1_M2CVariableMGTREFCLK1_112LVDSAU10AU9Table7:MGTCLK_M2CConnections3.

5.

5FMC-CarrierSignalClocks(GCLK_M2C)TheFMCinterfaceutilizesnumerousclockcapableandclockdedicatedconnectionsbetweentheFPGAandtheFMCmodule.

TheADM-VPX3-7V2connectsallpossibleclockpinsontheFMCinterfacetoclockcapabelIOontheFPGA.

PleaseseeAppendixClockPinsformoredetails.

3.

5.

625MHzSourceEarlyboardrevisionsusedaFoxoscillator,typeFXO-LC526R-25.

00,whichhastotalstability=±25ppm.

CurrentmodelsusetheSiLabs511FCA25M0000BA9,withhastotalstability=±30ppm.

Page11FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

6FlashMemoryA512MbFlashMemory(Intel/NumonyxPC28F512P30EF)isusedtostoreconfigurationbitstreamsfortheBridgeandTargetFPGAs.

TheflashmemorycannotbeaccessedbythetargetFPGA.

HostaccessisonlypossiblethroughtheFLCTL,FLPAGEandFLDATAregistersintheBridgeFPGA.

Theregionofmemorybetweenaddresses0x11000000and0x11FFFFFisallocatedforcustomdatatobestoredbytheADM-VPX3-7V2user.

Utilitiesforerasing,programmingandverificationoftheflashmemoryareprovidedintheADMXRCSDK.

WriteProtectTheFlashWriteProtect(WP#)pinisconnectedtoaninvertedversionoftheNVMROsignalattheXMCinterface.

WhentheNVMROsignalisactive(High),allwritestotheflashwillbeinhibited.

ThisstatewillbeindicatedbytheAmberLEDasshowninFigureLEDLocations.

Figure8:FlashMemoryMapPage12FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

7Configuration3.

7.

1Power-UpSequenceIfvaliddataisstoredintheflashmemory,thebridgewillautomaticallyconfiguretheTargetFPGAatpower-up.

ThissequencecanbeinhibitedbyturningtheFlashBootInhibit(FBI)switch.

(SeeTableSwitchDefinitions).

Note:Ifanover-temperaturealertisdetectedfromtheSystemMonitor,thetargetwillbeclearedbypulsingitsPROGsignal.

SeeSectionAutomaticTemperatureMonitoring.

3.

7.

2Bridge-LessModeWhenoperatinginbridgelessmode,theTargetFPGAwillbeconfigureddirectlybyaQuadSPIconnectiontoa512MbFLASHmemorydevice.

Thismemorydeviceisre-programableoveraXilinxJTAGcable.

Page13FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

8HealthMonitoringTheADM-VPX3-7V2hastheabilitytomonitortemperatureandvoltagetomaintainacheckontheoperationoftheboard.

ThemonitoringisimplementedusingtheATMEGA128microcontroller.

ControlalgorithmswithinthemicrocontrollerautomaticallychecklinevoltagesandonboardtemperaturesandsharestheinformationwithblockramintheBridgeFPGA.

Thefollowingvoltagerailsandtemperaturesaremonitored:MonitorPurpose1.

0VFPGACoreSupply(VccINT)1.

0VTargetTransceiverPower(AVCC)1.

2VTargetTransceiverPower(AVTT)1.

2VBridgeTransceiverPower(AVTT)1.

5VDDR3SDRAM,TargetFPGAmemoryI/OFMC_VADJ(Front-Panel)I/Ovoltage(1.

8Vorlower)1.

8VTargetTransceiverPower(AVCC_AUX)1.

8VFlashMemory,FPGAIOVoltage(VCCO)2.

0VTargetFPGAAuxiliarySupplyAUX(VccAUX)2.

5VLevelTranslation,BridgeFPGAAuxiliarySupply(VccAUX)3.

3VFromVPXP05.

0VFromVPXP012.

0VFromVPXP0Temp1TargetFPGAon-dietemperatureTemp2Boardtemperaturesensoron-dietemperatureTemp3BridgeFPGAon-dietemperatureTable8:VoltageandTemperatureMonitorsAnexampleapplicationthatreadsthesystemmonitor("sysmon")isavailablewithintheSDK.

Page14FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

8.

1AutomaticTemperatureMonitoringAtpower-up,thecontrollogicsetsthetemperaturelimitsandresetstheLM87'sover-temperatureinterrupt.

ThetemperaturelimitsareshowninTableTemperatureLimits:.

TargetFPGABridgeFPGABoardMinMaxMinMaxMinMaxCommercial0degC+85degC0degC+85degC0degC+85degCExtended0degC+100degC0degC+100degC0degC+100degCIndustrial-40degC+100degC-40degC+100degC-40degC+100degCTable9:TemperatureLimitsImportant:Ifanytemperaturelimitisexceeded,theTargetFPGAisautomaticallycleared.

ThisisindicatedbytheGreenLED(TargetConfigured)switchingoffandthetwostatusLEDsshowingatemperaturefaultindication.

Thepurposeofthismechanismistoprotectthecardfromdamageduetoover-temperature.

Itispossiblethatitwillcausetheuserapplicationand,possibly,thehostcomputerto"hang".

3.

8.

2MicrocontrollerStatusLEDsLEDsD7(Red)andD8(Green)indicatethemicrocontrollerstatus.

LEDsStatusGreenRunningandnoalarmsGreen+RedStandby(Poweredoff)FlashingGreen+FlashingRed(together)Attention-criticalalarmactiveFlashingGreen+FlashingRed(alternating)ServiceModeFlashingGreen+RedAttention-alarmactiveRedMissingapplicationfirmwareorinvalidfirmwareFlashingRedFPGAconfigurationclearedtoprotectboardTable10:StatusLEDDefinitionsPage15FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

9LocalBusAMultiplexedPacketTransportlink(MPTL)connectstheBridgeandTargetFPGAs.

Itiscapableoftransferringdataatupto2GB/ssimultaneouslyineachdirection.

TheMPTLreplacestheparallellocalbususedinpreviousgenerationsoftheADM-XRCseries.

DetailsofthelinkandexampledesignsaregivenintheSoftwareDevelopmentKit(SDK).

3.

10TargetFPGA3.

10.

1TargetFPGACharacteristicsTheADM-VPX3-7V2supportsVirtex-7V585T,V2000T,VX330T,VX485T,andVX690TdevicesintheFF(G),FH(G),andFLG(G)1761packages.

ThedistinguishingcharacteristicsofthesedevicesaredescribedinTableTargetFPGACharacteristics.

ThesefiguresaretakenfromtheVirtex-7FPGAFeatureSummaryavailableintheXilinx7seriesOverview.

ThemaximumuserI/OtotheVPXbackplanedoesnotchangewithdeviceselected.

HoweverFMCuserI/OisreducedsignificanlywithVX330TandVX485Tdevices.

DeviceLogicCellsSlicesDistributedRAMDSPSlicesBlockRAMCMTsPCIeHardMacrosXC7VX330T326,40051,0004,388Kb1,12027,000Kb142Gen3XC7VX485T485,76075,9008,175Kb2,80037,080Kb144Gen2XC7VX690T693,120108,30010,888Kb3,60052,920Kb203Gen3XC7V585T582,72091,0506,938Kb1,26028,620Kb183Gen2XC7V2000T1,954,560305,40021,550Kb2,16046,512Kb244Gen2Table11:TargetFPGACharacteristics3.

10.

2I/OBankVoltagesTheTargetFPGAIOisarrangedinbanks,eachwiththeirownsupplypins.

Thebanknumbers,theirvoltageandfunctionareshowninTableTargetFPGAIOBanks.

FulldetailsoftheIOSTANDARDrequiredforeachsignalaregivenintheSDK.

IOBanksVoltagePurpose0,141.

8VConfiguration,JTAG,LBusControl,TargetSelectMapInterface131.

8VRGMIIto1000Base-X391.

8VP2GPIO31,32,33FMC_VADJFMCInterface(variablevoltage,1.

8Vmax)12FMC_VIO_BFMCInterface(variablevoltage,1.

8VMax)15,16,18,19,34,35,37,381.

5VDRAMBanks0-3Table12:TargetFPGAIOBanksPage16FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

10.

3TargetMGTLinksThereareatotalof34Multi-GigabitTransceiver(MGT)linksconnectedtotheTargetFPGA:LinksWidthConnectionPCIe(3:0)4BridgeFPGA(forMPTL)orVPXP1Wafers1-4inBridgeBypassModePCIe(7:4)4DirectlinktoVPXP1Wafers5-8P1Expansion(3:0)4DirectlinktoVPXP1Wafer9-12UserDefined(11:0)12DirectlinktoVPXP2Wafer7-16andVPXP1Wafers13and14FMCMGT(9:0)10DirectlinktoFMCinterfaceTable13:TargetMGTLinksTheconnectionsoftheselinksareshowninFigureADM-VPX3-7V2BlockDiagram:ForMGTClockingseeFigureClocks:Page17FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

11MemoryInterfacesTheADM-VPX3-7V2hasfourindependentbanksofDDR3SDRAM.

Eachbankconsistsoftwo16bitwidememorydevicesinparalleltoprovidea32bitdatapathcapableofrunningupto800Hz(DDR-1600).

2Gbdevices(MicronMT41K128M16JT-125)arefittedasstandardtoprovide512MBperbank.

4Gb(giving1GBperbank)and8Gb(2GBperbank)areavailableasanorderingoption.

ThememorybanksarearrangedforcompatibilitywiththeXilinxMemoryInterfaceGenerator(MIG).

FigureDRAMBanksShowsthecomponentreferencesandFPGAbanksused.

Fulldetailsoftheinterface,signalingstandardsandanexampledesignareprovidedintheSDK.

Figure9:DRAMBanksSpeedGradeSingleRank(2GB-8GB)-31600-2/-2L/-2G1600-11600-1M1066Table14:MaximumMemorySpeedsPage18FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust20163.

12FMCInterfaceandFront-PanelI/OTheFMCinterfaceprovidesahigh-performanceandflexiblefront-panelinterfacethrougharangeofinterchangeable,industrystandardIOmoduleswhichconnectatreceptacleJ3.

TheFMCinterfaceadherestoVITA57.

1.

TheADM-VPX3-7V2utilizesallpossibleFMCconnectivity.

ThisincludesallGPIO,allMGTlinks,andallclockcapableIO.

FMCI2Csignal(SCLandSDAatC30andC31)areconnectedtothesystemmonitormicrocontroller.

Theyareusedtodetermineoperatingvoltageduringstartupandarenotaccesabletotheuser.

TheFMCPresentsignal(PRSNT_M2C_LatconnectorpinH2)isbufferedtoFPGApinAN33whichisa1.

8VcompatibleIOpin.

Note:TheADM-VPX3-7V2supportsonly1.

8VandlowerVADJVoltages.

Note:IfVX330TorVX485TFPGAsareselectedasthetarget,theFMCinterfacewilllosesignificantfunctionality.

Seepinassignmentsfordetails.

Page19FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016PageIntentionallyleftblankPage20FunctionalDescriptionad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixA:P1PinAssignmentsAppendixA.

1:DataPlane(P1Wafers1-4)SignalVPXP1FPGA|FPGAVPXP1SignalPCIE_TX0_PorLLINK_T2B0_PD1J2|H8A1PCIE_RX0_PorLLINK_B2T0_PPCIE_TX0_NorLLINK_T2B0_NE1J1|H7B1PCIE_RX0_NorLLINK_B2T0_NPCIE_TX1_PorLLINK_T2B1_PE2H4|G6B2PCIE_RX1_PorLLINK_B2T1_PPCIE_TX1_NorLLINK_T2B1_NF2H3|G5C2PCIE_RX1_NorLLINK_B2T1_NPCIE_TX2_PorLLINK_T2B2_PD3G2|F8A3PCIE_RX2_PorLLINK_B2T2_PPCIE_TX2_NorLLINK_T2B2_NE3G1|F7B3PCIE_RX2_NorLLINK_B2T2_NPCIE_TX3_PorLLINK_T2B3_PE4F4|E6B4PCIE_RX3_PorLLINK_B2T3_PPCIE_TX3_NorLLINK_T2B3_NF4F3|E5C4PCIE_RX3_NorLLINK_B2T3_NTable15:DataPlane(P1Wafers1-4)Note:ThisbusisonlyconnectedtothetargetFPGAwheninBridgeBypassmode.

OtherwisethisbusisconnectedtotheAlphaDataBridge.

SeeTableSwitchDefinitionsforBridgeBypassmodedetails.

AppendixA.

2:Data/ExpansionPlane(P1Wafers5-8)SignalVPXP1FPGA|FPGAVPXP1SignalPCIE_TX4_PD5K4|J6A5PCIE_RX4_PPCIE_TX4_NE5K3|J5B5PCIE_RX4_NPCIE_TX5_PE6L2|L6B6PCIE_RX5_PPCIE_TX5_NF6L1|L5C6PCIE_RX5_NPCIE_TX6_PD7M4|N6A7PCIE_RX6_PPCIE_TX6_NE7M3|N5B7PCIE_RX6_NPCIE_TX7_PE8N2|P8B8PCIE_RX7_PPCIE_TX7_NF8N1|P7C8PCIE_RX7_NTable16:Data/ExpansionPlane(P1Wafers5-8)Page21P1PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixA.

3:Expansion/UserPlane(P1Wafers9-14)SignalVPXP1FPGA|FPGAVPXP1SignalP1_TX0_PD9E2|D8A9P1_RX0_PP1_TX0_NE9E1|D7B9P1_RX0_NP1_TX1_PE10D4|C6B10P1_RX1_PP1_TX1_NF10D3|C5C10P1_RX1_NP1_TX2_PD11C2|B8A11P1_RX2_PP1_TX2_NE11C1|B7B11P1_RX2_NP1_TX3_PE12B4|A6B12P1_RX3_PP1_TX3_NF12B3|A5C12P1_RX3_NP1_TX4_PD13AH4|AE6A13P1_RX4_PP1_TX4_NE13AH3|AE5B13P1_RX4_NP1_TX5_PE14AG2|AD4B14P1_RX5_PP1_TX5_NF14AG1|AD3C14P1_RX5_NTable17:Expansion/UserPlane(P1Wafers9-14)AppendixA.

4:ControlPlane(P1Wafers15-16)SignalVPXP1Component.

Pin|Component.

PinVPXP1SignalETH2_TX_PD15U10.

4|U10.

1A15ETH2_RX_PETH2_TX_NE15U10.

5|U10.

2B15ETH2_RX_NETH1_TX_PE16U11.

4|U11.

1B16ETH1_RX_PETH1_TX_NF16U11.

5|U11.

2C16ETH1_RX_NTable18:ControlPlane(P1Wafers15-16)Thecontrolplane1000Base-XEthernetonWafer16iscontrolledbythetargetFPGAusinganRGMIIinterfacetoaMarvell88E1512.

SeepinassignmentbelowforRGMIIconnectivitydetails.

SignalFPGA|FPGASignalETH1_TXD0AW36|AT36ETH1_RXD0ETH1_TXD1AV36|AT34ETH1_RXD1ETH1_TXD2AY34|AU34ETH1_RXD2ETH1_TXD3BA35|AU36ETH1_RXD3ETH1_TX_CTRLBA34|AT32ETH1_RX_CTRLETH1_TX_CLKAW32|AV34ETH1_RX_CLKETH1_MDCAU32|AV33ETH1_MDIOETH1_CLK125AY32|--Table19:RGMIIto1000Base-XPHYPage22P1PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixB:P2PinAssignmentsAppendixB.

1:GPIO24s/12d+8s(P2Wafers1-6)SignalVPXP2FPGA|FPGAVPXP2SignalGP1_PE6C16|B16F6GP1_NGP2_PB6C15|C14C6GP2_NGP3_PD5B14|A14E5GP3_NGP4_PA5D16|D15B5GP4_NGP5_PE4D13|C13F4GP5_NGP6_PB4E12|D12C4GP6_NGP7_PD3F16|E15E3GP7_NGP8_PA3G12|F12B3GP8_NGP9_PE2E14|E13F2GP9_NGP10_PB2J13|H13C2GP10_NGP11_PD1F15|F14E1GP11_NGP12_PA1H16|G16B1GP12_NGP13G1M13|N14G3GP14GP15G5N13|N15G7GP16GP17G9N16|M12G11GP18GP19G13M11|M16G15GP20Table20:GPIO24s/12d+8s(P2Wafers1-6)Allsingleendedpinscanfunctionaspush-pullupto60MbpsorOpen-drainupto2Mbps.

DifferentialoperationislimitedonlybyFPGAIOpins.

SwitchingbetweenSingleEndedanddifferentialsignalingisdescribedinTableSwitchDefinitions.

Page23P2PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixB.

2:MGTLanes20d(P2Wafers7-16)SignalVPXP2FPGA|FPGAVPXP2SignalP2_TX0_PD7U2|W6A7P2_RX0_PP2_TX0_NE7U1|W5B7P2_RX0_NP2_TX1_PE8T4|V4B8P2_RX1_PP2_TX1_NF8T3|V3C8P2_RX1_NP2_TX2_PD9R2|U6A9P2_RX2_PP2_TX2_NE9R1|U5B9P2_RX2_NP2_TX3_PE10P4|R6B10P2_RX3_PP2_TX3_NF10P3|R5C10P2_RX3_NP2_TX4_PD11AE2|AC6A11P2_RX4_PP2_TX4_NE11AE1|AC5B11P2_RX4_NP2_TX5_PE12AC2|AB4B12P2_RX5_PP2_TX5_NF12AC1|AB3C12P2_RX5_NP2_TX6_PD13AA2|AA6A13P2_RX6_PP2_TX6_NE13AA1|AA5B13P2_RX6_NP2_TX7_PE14W2|Y4B14P2_RX7_PP2_TX7_NF14W1|Y3C14P2_RX7_NP2_TX8_PD15AK4|AG6A15P2_RX8_PP2_TX8_NE15AK3|AG5B15P2_RX8_NP2_TX9_PE16AJ2|AF4B16P2_RX9_PP2_TX9_NF16AJ1|AF3C16P2_RX9_NTable21:MGTLanes20d(P2Wafers7-16)Page24P2PinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixC:FMCPinAssignmentsAppendixC.

1:GPIOPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalLA00_CC_PG6AU23|AV23G7LA00_CC_NLA01_CC_PD8AT22|AU22D9LA01_CC_NLA02_PH7AM24|AN24H8LA02_NLA03_PG9AJ23|AK23G10LA03_NLA04_PH10AK20|AL20H11LA04_NLA05_PD11AL21|AM21D12LA05_NLA06_PC10AJ21|AJ20C11LA06_NLA07_PH13AR24|AT24H14LA07_NLA08_PG12AM23|AN23G13LA08_NLA09_PD14AP23|AP22D15LA09_NLA10_PC14AN21|AP21C15LA10_NLA11_PH16BA22|BB22H17LA11_NLA12_PG15AT21|AU21G16LA12_NLA13_PD17AV21|AW21D18LA13_NLA14_PC18BA21|BB21C19LA14_NLA15_PH19AY24|BA24H20LA15_NLA16_PG18BB24|BB23G19LA16_NLA17_CC_PD20AW23|AW22D21LA17_CC_NLA18_CC_PC22AR23|AR22C23LA18_CC_NLA19_PH22AU24|AV24H23LA19_NLA20_PG21AY25|BA25G22LA20_NLA21_PH25AJ22|AK22H26LA21_NLA22_P*G24AU19|AV19G25LA22_N*LA23_P*D23AR18|AR17D24LA23_N*LA24_P*H28AN19|AN18H29LA24_N*LA25_P*G27AP20|AR19G28LA25_N*LA26_P*D26AV16|AW16D27LA26_N*LA27_P*C26AT20|AT19C27LA27_N*LA28_P*H31AK19|AK18H32LA28_N*LA29_P*G30AL19|AM19G31LA29_N*LA30_P*H34AK17|AL17H35LA30_N*Table22:GPIOPins(continuedonnextpage)Page25FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SignalFMC(J1)FPGA|FPGAFMC(J1)SignalLA31_P*G33AM18|AM17G34LA31_N*LA32_P*H37AP18|AP17H38LA32_N*LA33_P*G36AM16|AN16G37LA33_N*HA00_CC_P*F4AV13|AW13F5HA00_CC_N*HA01_CC_P*E2AU14|AU13E3HA01_CC_N*HA02_P*K7AJ16|AJ15K8HA02_N*HA03_P*J6AJ13|AJ12J7HA03_N*HA04_P*F7AK14|AK13F8HA04_N*HA05_P*E6AK15|AL14E7HA05_N*HA06_P*K10AL16|AL15K11HA06_N*HA07_P*J9AM12|AM11J10HA07_N*HA08_P*F10AN11|AP11F11HA08_N*HA09_P*E9AM13|AN13E10HA09_N*HA10_P*K13AN15|AN14K14HA10_N*HA11_P*J12AP12|AR12J13HA11_N*HA12_P*F13AY14|AY13F14HA12_N*HA13_P*E12AW12|AY12E13HA13_N*HA14_P*J15BB14|BB13J16HA14_N*HA15_P*F16BA15|BA14F17HA15_N*HA16_P*E15AV15|AV14E16HA16_N*HA17_CC_P*K16AP13|AR13K17HA17_CC_N*HA18_P*J18BA16|BB16J19HA18_N*HA19_P*F19AR15|AT15F20HA19_N*HA20_P*E18AR14|AT14E19HA20_N*HA21_P*K19AT12|AU12K20HA21_N*HA22_P*J21AY19|BA19J22HA22_N*HA23_P*K22AY20|BA20K23HA23_N*HB00_CC_P*K25AR27|AT27K26HB00CC__N*HB01_P*J24BA26|BA27J25HB01_N*HB02_P*F22AV25|AV26F23HB02_N*HB03_P*E21BB26|BB27E22HB03_N*HB04_P*F25AY27|AY28F26HB04_N*HB05_P*E24BB28|BB29E25HB05_N*HB06_CC_P*K28AU26|AU27K29HB06_CC_N*HB07_P*J27AW27|AW28J28HB07_N*HB08_P*F28AU29|AV29F29HB08_N*Table22:GPIOPins(continuedonnextpage)Page26FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016SignalFMC(J1)FPGA|FPGAFMC(J1)SignalHB09_P*E27AW25|AW26E28HB09_N*HB10_P*K31AR29|AT29K32HB10_N*HB11_P*J30AU28|AV28J31HB11_N*HB12_P*F31AN28|AP28F32HB12_N*HB13_P*E30AT25|AT26E31HB13_N*HB14_P*K34AL25|AL26K35HB14_N*HB15_P*J33AM26|AM27J34HB15_N*HB16_P*F34AK27|AL27F35HB16_N*HB17_CC_P*K37AP27|AR28K38HB17_CC_N*HB18_P*J36AK24|AK25J37HB18_N*HB19_P*E33AP25|AR25E34HB19_N*HB20_P*F37AN25|AN26F38HB20_N*HB21_P*E36AJ25|AJ26E37HB21_N*FMC_CLK_DIR_1V8*B1BB12|---Table22:GPIOPinsAppendixC.

2:ClockPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalGBTCLK0_M2C_P*D4AT8|AT7D5GBTCLK0_M2C_N*GBTCLK1_M2C_P*B20AU10|AU9B21GBTCLK1_M2C_N*CLK0_M2C_P*H4AY18|AY17H5CLK0_M2C_N*CLK1_M2C_P*G2AT17|AU17G3CLK1_M2C_N*CLK2_BIDIR_P*K4AU18|AV18K5CLK2_BIDIR_N*CLK3_BIDIR_P*J2AW18|AW17J3CLK3_BIDIR_N*Table23:ClockPins*ForXCVX330TorXCVX485TpinsnotconnectedPage27FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016AppendixC.

3:MGTPinsSignalFMC(J1)FPGA|FPGAFMC(J1)SignalDP0_M2C_PC6AN6|AP4C2DP0_C2M_PDP0_M2C_NC7AN5|AP3C3DP0_C2M_NDP1_M2C_PA2AM8|AN2A22DP1_C2M_PDP1_M2C_NA3AM7|AN1A23DP1_C2M_NDP2_M2C_PA6AL6|AM4A26DP2_C2M_PDP2_M2C_NA7AL5|AM3A27DP2_C2M_NDP3_M2C_PA10AJ6|AL2A30DP3_C2M_PDP3_M2C_NA11AJ5|AL1A31DP3_C2M_NDP4_M2C_P*A14AV8|AV4A34DP4_C2M_P*DP4_M2C_N*A15AV7|AV3A35DP4_C2M_N*DP5_M2C_P*A18AU6|AU2A38DP5_C2M_P*DP5_M2C_N*A19AU5|AU1A39DP5_C2M_N*DP6_M2C_P*B16AR6|AT4B36DP6_C2M_P*DP6_M2C_N*B17AR5|AT3B37DP6_C2M_N*DP7_M2C_P*B12AP8|AR2B32DP7_C2M_P*DP7_M2C_N*B13AP7|AR1B33DP7_C2M_N*DP8_M2C_P*B8BB8|BB4B28DP8_C2M_P*DP8_M2C_N*B9BB7|BB3B29DP8_C2M_N*DP9_M2C_P*B4BA6|BA2B24DP9_C2M_P*DP9_M2C_N*B5BA5|BA1B25DP9_C2M_N*Table24:MGTPins*ForXCVX330TorXCVX485TpinsnotconnectedPage28FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016RevisionHistoryDateRevisionChangedByNatureofChange10Oct20120.

1K.

RothInitialDraft14Mar20131.

0K.

RothInitialRelease,finalizedappendix29Oct20131.

1K.

RothUpdatedFigureClocksto25MHzonboardoscilator,TablePROGCLKConnectionsfixedtoshowPROGCLK[4:0]insteadof[3:0],UpdatedmiscellaneousAppendixtablecolumnheaderstoshowVPXP1whereappropriate.

14Nov20131.

2K.

RothUpdatedSectionAUXCLKtoshowpinassignments.

19Nov20131.

3K.

RothUpdatedFigureADM-VPX3-7V2BlockDiagramandTableRGMIIto1000Base-XPHY.

23Jan20141.

4K.

RothAddedSectionVPXP2GPIO6Feb20141.

5K.

RothCorrectedPROGCLK0andPROGCLK1inClocks18Feb20141.

6K.

RothChangedSystemRequirementstospecify5.

0VasthedefaultVPWRoption.

8Jul20141.

7K.

RothAddedAutomaticTemperatureMonitoringandMaximumMemorySpeeds16Oct20151.

8K.

RothUpdatedJTAGInterfacetocorrectJ3referencedesignation,FMCInterfaceandFront-PanelI/OtoincludeFMCPresentandI2Cdescription,andadded25MHzSource.

22Aug20161.

9K.

RothUpdatedMemoryInterfacestoremovedualrank8Gboptionasmicronhasmovedthisparttosinglerank.

Page29FMCPinAssignmentsad-ug-1255_v1_9.

pdfADM-VPX3-7V2UserManualV1.

9-22ndAugust2016PageIntentionallyleftblankAddress:4WestSilvermillsLane,Edinburgh,EH35BD,UKTelephone:+441315582600Fax:+441315582700email:sales@alpha-data.

comwebsite:http://www.

alpha-data.

comAddress:3507RingsbyCourtSuite105,Denver,CO80216Telephone:(303)9548768Fax:(866)8209956tollfreeemail:sales@alpha-data.

comwebsite:http://www.

alpha-data.

com4.

5

- REFCLK200M_HSTLavtt.info相关文档

- 红帽avtt.info

- ncavtt.info

- 百家讲坛avtt.info

- 您的avtt.info

- 2.5avtt.info

- peopleavtt.info

一键去除宝塔面板各种计算题与延时等待

现在宝塔面板真的是越来越过分了,删除文件、删除数据库、删除站点等操作都需要做计算题!我今天升级到7.7版本,发现删除数据库竟然还加了几秒的延时等待,也无法跳过!宝塔的老板该不会是小学数学老师吧,那么喜欢让我们做计算题!因此我写了个js用于去除各种计算题以及延时等待,同时还去除了软件列表页面的bt企业版广告。只需要执行以下命令即可一键完成!复制以下命令在SSH界面执行:Layout_file="/w...

vdsina:俄罗斯VPS(datapro),6卢布/天,1G内存/1核(AMD EPYC 7742)/5gNVMe/10T流量

今天获得消息,vdsina上了AMD EPYC系列的VDS,性价比比较高,站长弄了一个,盲猜CPU是AMD EPYC 7B12(经过咨询,详细CPU型号是“EPYC 7742”)。vdsina,俄罗斯公司,2014年开始运作至今,在售卖多类型VPS和独立服务器,可供选择的有俄罗斯莫斯科datapro和荷兰Serverius数据中心。付款比较麻烦:信用卡、webmoney、比特币,不支持PayPal...

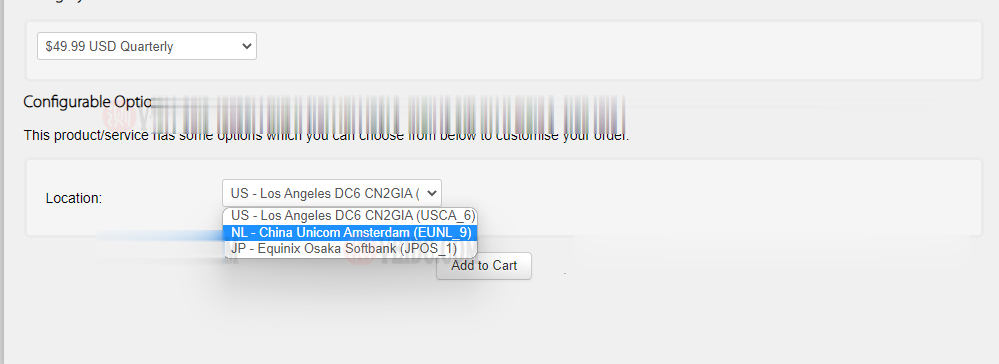

搬瓦工:新增荷兰机房 EUNL_9 测评,联通 AS10099/AS9929 高端优化路线/速度 延迟 路由 丢包测试

搬瓦工最近上线了一个新的荷兰机房,荷兰 EUNL_9 机房,这个 9 的编号感觉也挺随性的,之前的荷兰机房编号是 EUNL_3。这次荷兰新机房 EUNL_9 采用联通 AS9929 高端路线,三网都接入了 AS9929,对于联通用户来说是个好消息,又多了一个选择。对于其他用户可能还是 CN2 GIA 机房更合适一些。其实对于联通用户,这个荷兰机房也是比较远的,相比之下日本软银 JPOS_1 机房可...

avtt.info为你推荐

-

网易网盘关闭入口如何快速开通网易网盘?brandoff淘宝上的代购奢侈品都是真品吗?美国互联网瘫痪2000年美国的互联网危机事件的原因?梦之队官网NBA梦之队在哪下载?曲妙玲张婉悠香艳版《白蛇传》是电影还是写真集?rawtools照片上面的RAW是什么意思,为什么不能到PS中去编辑www.622hh.comwww.710av.com怎么不可以看了www.haole012.comhttp://fj.qq.com/news/wm/wm012.htm 这个链接的视频的 第3分20秒开始的 背景音乐 是什么?www.e12.com.cn有什么好的高中学习网?99nets.com99nets网游模拟娱乐社区怎么打不开了?????????谁能告诉我 ???、