main苹果5.1.1完美越狱

苹果5.1.1完美越狱 时间:2021-05-24 阅读:()

BSCAN1–MultipleScanPortAddressableBufferReferenceDesignFPGA-RD-02105-7.

4December2019BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

2FPGA-RD-02105-7.

4DisclaimersLatticemakesnowarranty,representation,orguaranteeregardingtheaccuracyofinformationcontainedinthisdocumentorthesuitabilityofitsproductsforanyparticularpurpose.

AllinformationhereinisprovidedASISandwithallfaults,andallriskassociatedwithsuchinformationisentirelywithBuyer.

Buyershallnotrelyonanydataandperformancespecificationsorparametersprovidedherein.

ProductssoldbyLatticehavebeensubjecttolimitedtestinganditistheBuyer'sresponsibilitytoindependentlydeterminethesuitabilityofanyproductsandtotestandverifythesame.

NoLatticeproductsshouldbeusedinconjunctionwithmission-orsafety-criticaloranyotherapplicationinwhichthefailureofLattice'sproductcouldcreateasituationwherepersonalinjury,death,severepropertyorenvironmentaldamagemayoccur.

TheinformationprovidedinthisdocumentisproprietarytoLatticeSemiconductor,andLatticereservestherighttomakeanychangestotheinformationinthisdocumentortoanyproductsatanytimewithoutnotice.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

43Contents1.

Introduction.

42.

FunctionalDescription.

53.

SignalDescriptions.

74.

BackplaneInterface.

85.

RegisterSet.

86.

AddressingScheme.

86.

1AddressingwithLevel1Protocol.

86.

1.

1.

DirectAddressing86.

2.

Level2Protocol.

96.

2.

1.

Level2InstructionTypes.

96.

2.

2.

Level2InstructionDescriptions107.

RegisterDescriptions.

107.

1.

InstructionRegister.

107.

2.

BoundaryScanRegister107.

3.

BypassRegister107.

4.

ModeRegister.

117.

5.

DeviceIdentificationRegister117.

6.

Reset.

128.

PortSynchronization139.

Implementation.

14Glossary15TechnicalSupportAssistance16RevisionHistory.

17FiguresFigure1.

1.

BSCAN1BlockDiagram4Figure2.

1.

InternalStateMachines.

5Figure2.

2.

IEEE1149.

1StateMachine5Figure2.

3.

SelectionControllerStateMachine.

6Figure2.

4.

LocalPortConfigurationStateMachine.

6Figure6.

1.

DirectAddressing:DeviceAddressLoadedintoInstructionRegister.

9Figure8.

1.

LocalScanPortSynchronizationonSecondPass13Figure8.

2.

SynchronizationoftheThreeLocalScanPorts(LSP1,LSP2andLSP3)13TablesTable3.

1.

SignalDescriptions.

7Table5.

1.

SignalDescriptions.

8Table6.

1.

DirectAddressMode9Table6.

2.

InstructionSet.

9Table7.

1.

ModeRegisterControlofLSP11Table7.

2.

DetailedDeviceIdentification(Binary)11Table7.

3.

ResetConfigurationforRegisters12Table9.

1.

PerformanceandResourceUtilization14BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

4FPGA-RD-02105-7.

41.

IntroductionBSCAN1isamultipleboundaryscantestaccessport(TAP)addressablebufferfunctionthatcanbeaccessedthroughastandardIEEE1149.

1interface.

WiththreeLocalScanPorts(LSP),theBSCAN1functioncanbestructuredashierarchicalportswiththeabilitytoaddandremovelocalscanchainstoimprovetestthroughput.

TheLSPcanalsobeaccessedindividuallyorincombinationoftwoorthreeportsatatimetostreamlinethetestflowofsimilardevices.

TheLSPsareconfiguredbyaccessingtheModeRegisterfromthemasterTAPinterface.

InadditiontothestandardTAPinterfacesignalsTDI,TMS,TCK,TDOandTRST,theBSCAN1interfacealsoincludessixstaticIDinputsandaTOEinput.

TheModeRegisterisusedtoconfigurethelocalscanports.

Itallowsdaisychainingand/orbypassingofthelocalscanports.

ThestaticIDinputsarecapableofsupportingupto64uniqueaddresses.

TheTOEsignalisusedtoenableordisableallthelocalscanports.

ThemajorfunctionalblocksandgeneralarchitectureofBSCAN1areillustratedinFigure1.

1.

AsdefinedinIEEE1149.

1,theinstructionregisterandvarioustestdataregisterscanbescannedtoexercisethefunctionsofBSCAN1.

The16-statestatemachineTAPController,hereaftercalledtheMasterTAPController,providesthemaincontrolforthedevice.

Figure1.

1.

BSCAN1BlockDiagramTheprimaryfunctionofthePortSelectionControlleristocomparetheaddressshiftedintotheInstructionRegistertothestaticidentificationinputs,allowingthe1149.

1protocoltobeusedwithinamultidropenvironment.

ItthenenablesBSCAN1,asappropriate,forotheroperations.

MultiplexinglogicforselectingdifferentportconfigurationsiscontainedintheLocalScanPort(LSP).

TheBSCAN1instructionregister,moderegisterandtheTAPControllerallprovideinputintotheLocalScanControllerblock.

AllfourTAPboundaryscansignalsarethenfedbytheLocalScanControllerfromtheirrespectiveportstothelocalscanports.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

452.

FunctionalDescriptionInamultidropscansystem,thescantesterhastheabilitytoselectindividualBSCAN1devicesasneededforscanoperations.

ScanchainsareselectedwhenaparticulardeviceaddressissenttoallBSCAN1devices.

Thedevicewiththecorresponding,hardcodedaddressisenabledtoreceiveinstructionsfromthescantester.

Thisselectionisdoneusinga"Level1"protocol(seeGlossary)andsubsequentinstructionsaresenttotheappropriateBSCAN1byusinga"Level2"protocol.

AsisdescribedinFigure2.

1.

,BSCAN1containsan1149.

1TAPControlStateMachine(Figure2.

2.

),aSelectionStateMachine(Figure2.

3.

)andaPortConfigurationStateMachine(identicalforeachlocalport,seeFigure2.

4.

).

Figure2.

1.

InternalStateMachinesFigure2.

2.

IEEE1149.

1StateMachineBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

6FPGA-RD-02105-7.

4Figure2.

3.

SelectionControllerStateMachineFigure2.

4.

LocalPortConfigurationStateMachineTheSelectionStateMachineisresponsiblefortheaddressingandmultidropcapability.

Italsosupportsfunctionalityforsingleaccessandthechip'sLevel1protocol.

ThePortConfigurationStateMachineallowstheindividualenablinganddisablingoftheLSPsfromtheoverallscanchain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

47ThePortConfigurationStateMachinecontrolswhichlocalscanportsareincludedin,andwhichportsareisolatedfrom,theoverallscanchain.

Therefore,tothesystemscancontroller,eachBSCAN1representsonlyasinglescanchain.

InternaltoBSCAN1isthelogicthatcontrolswhichorhowmanyoftheLSPsareincludedinthechainpresentedtothesystemscancontroller.

Therearetwostablestatesinwhichalocalportcanbeparked:Parked-TLRandParked-RTI.

Onceachainisparked,itisremovedfromtheactivescanchainindefinitely,oruntil"unparked.

"Unparkingachainmovesitintotheactivechain.

AsisshowninFigure2.

4.

,thestateofeachofthelocalportsisindependentofthestatesofotherlocalportsonBSCAN1.

ItisimportanttounderstandthatsomestatesdependonthecurrentstateoftheTAPControllerStateMachine,whileinothersthestateofBSCAN1'sTAPControlStateMachinecanbeforcedbytransitionsofthePortConfigurationStateMachine.

BSCAN1'sPortConfigurationStateMachineprovidespartoftheLevel2protocolandhasanumberofLevel2instructionsotherthanlocalscanportconfigurationthatprovideaccesstoandcontrolofvariousregisterswithinBSCAN1.

Theinstructionsinclude:BYPASSEXTESTSAMPLE/PRELOADIDCODEMODESELGOTOWAITEachBSCAN1canbeselectedindividually.

Level2protocolcommandsareusedtoparkorunpark.

Afterareset,BSCAN1isreadyforLevel1protocolandLevel2protocolinstructions,inthatorder.

TheTAPcontrollerstatemachineisresettotheTLR(Test-Logic-Reset)state,thePortSelectionStateMachineisintheWait-for-AddressstateandthethreelocalscanportsareintheParked-TLRstate.

3.

SignalDescriptionsTable3.

1.

SignalDescriptionsPinI/ODescriptionTCKITestclockinputfromthebackplane.

ThisisthemasterclocksignalthatcontrolsallscanoperationsofBSCAN1andofthethreelocalscanports.

TMSITestmodeselectinputfromthebackplane.

ControlssequencingthroughtheTAPcontrollerofBSCAN1.

AlsocontrolssequencingoftheTAPsonthethreelocalscanchains.

TDIITestdatainputfromthebackplane.

AllbackplanescandataissuppliedtoBSCAN1throughthisinputpin.

TDOOTestdataoutputtothebackplane.

ThisoutputdrivestestdatafromBSCAN1backtothemastercontroller.

TRSTITestreset.

Anactive-low,asynchronousresetsignal,whichinitializestheBSCAN1logic.

SEL[0:5]IStaticidentificationinput.

TheconfigurationofthesesixpinsisusedtoassignauniqueaddresstoeachBSCAN1onthesystembackplane.

TOEITestoutputenable.

Whenhigh,thelocalscanportsareenabled.

Whenlow,forcesthelocalscanportstotristate.

Thisenablesanalternateresourcetoaccessoneormoreofthethreelocalscanchains.

TCK[1:3]OLocaltestclockoutputs.

Individualoutputtoeachofthethreelocalscanports.

Thesearebufferedver-sionsofTCK.

TMS[1:3]OLocaltestmodeselectoutputs.

Individualoutputtoeachofthethreelocalscanports.

TDI[1:3]ILocaltestdatainputs.

Individualscandatainputfromeachofthethreelocalscanports.

TDO[1:3]OLocaltestdataoutputs.

Individualscandataoutputtoeachofthethreelocalscanports.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

8FPGA-RD-02105-7.

44.

BackplaneInterfaceViaitsbackplaneport,BSCAN1receivesinstructionsfromtheIEEE1149.

1tester.

BSCAN1enterstheWait-for-Addressstatefollowingthetestlogicreset.

DataisshiftedinthroughtheTDIinputandintotheBSCAN1InstructionregisterwhentheTAPcontrollerissequencedtotheShift-IRstate.

NotethatifBSCAN1isnotproperlyaddressedandsuccessfullyselected,nodataisshiftedoutoftheinstructionregister.

Instead,asdataisshiftedintotheinstructionregister,thedatashiftedoutisdiscardedratherthanexitingthroughtheTDOoutput.

Uponupdatingtheinstructionregisterwiththeaddressdata,thescanned-inaddressiscomparedwiththesixleastsignificantbitsoftheIRandthestaticaddresssignalsSEL(0-5)(seeFigure6.

1.

).

Ifnoaddressmatchisdetected,thedeviceentersanunselectedstate.

Whenanaddressismatched,itenterstheselectedstate.

Level2protocolisusedtoissuecommandsandaccessregistersonceaBSCAN1hasbeenselected.

5.

RegisterSetSelectionandconfiguration,scandatamanipulationandscansupportoperationsregisterscanallbegroupedasshowninTable5.

1.

Whenaregisterisselected,dataentersthroughtheMSBandisshiftedoutthroughthescaninputofthenextdeviceinthedaisychain(seeTable7.

1.

).

Table5.

1.

SignalDescriptionsRegisterNameSignalDescriptionInstructionRegisterAddressingandinstructiondecodeIEEEStandard1149.

1requiredregisterBoundaryscanRegisterIEEEStandard1149.

1requiredregisterBypassRegisterIEEEStandard1149.

1requiredregisterDeviceIdentificationRegisterIEEEStandard1149.

1requiredregisterModeRegisterLocalportconfigurationandcontrolbits6.

AddressingSchemeThebasicfunctionofBSCAN1istoallowalargeorcomplexsystemtobedividedintosmallerblocksfortestingpurposes.

AcentraltestcontrollerisnetworkedwithoneormoreBSCAN1devicesandgiventhecapabilitytoaddressindividualBSCAN1devices.

Bothmultidropandhierarchicalconnectivityaresupportedandthetestcontrollercandynamicallyselectanypartofthenetwork.

BSCAN1supportstwolevelsofpartitioning.

ALevel1protocolsupportstheselectionofoneBSCAN1device.

Withineachdevice,aLevel2protocolsupportstheselectionofindividualports.

TheselectedportsoftheindividualdevicearethenpresentedasasinglechainthatcanbeincludedinthefinalnetworkoftheselectedBSCAN1device.

6.

1.

AddressingwithLevel1ProtocolOnemodeofaddressingissupportedbyBSCAN1.

IndividualBSCAN1devicescanbeselectedinthe"single"mode,alsoknownasDirectAddressing.

6.

1.

1.

DirectAddressingBSCAN1enterstheWait-for-Addressstatewhen:(1)ItsTAPControllerenterstheTest-Logic-Resetstate,or(2)ItsinstructionregisterisupdatedwiththeGOTOWAITinstruction,whileeitherselectedorunselected.

WhileintheWait-for-Addressstate,theBSCAN1controllerreceivesdatashiftedinthroughtheinstructionregister.

IntheUpdate-IRstate,bits5through0oftheinstructionregisterarecomparedwiththestaticallyconfiguredaddressbitsSEL(0-5).

(EveryBSCAN1deviceinascannetworkmustbeindividuallysetwithauniqueaddressonitsSEL(0-5)inputs.

)ABSCAN1devicebecomesselected,oractiveinthechain,whenthesixleastsignificantbitsoftheinstructionregistermatchthestaticaddressbitsSEL(0-5)(Figure6.

1.

).

TheselecteddeviceisnowreadytoreceiveLevel2protocol.

Whenactive,theselecteddevice'sidentificationregisterisinsertedaspartoftheactivescanchain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

49Table6.

1.

DirectAddressModeAddressType/HexAddressBinaryAddressTDOStateDirectAddress00hto3FhXX000000btoXX111111bNormalIEEEStandard1149.

1Note:OnlythesixLSBsoftheaddressarecomparedtotheSEL(0-5)inputs.

ThetwoMSBsare"don'tcares".

Figure6.

1.

DirectAddressing:DeviceAddressLoadedintoInstructionRegisterUnselecteddevices(wherethestaticaddressdidnotmatchthesixLSBsoftheIR)willremainthatwayuntiltheirinstructionregisterisupdatedwiththeGOTOWAITinstructionortheirTAPcontrollerenterstheTest-Logic-Resetstate.

6.

2.

Level2ProtocolLevel2protocolfollowsIEEEstandard1149.

1TAPprotocol.

Afterbeingaddressedandselectedintheactivechain,theBSCAN1deviceisaccessedbyLevel2protocol.

OnceBSCAN1isselected,thelocalscanportsremainparkedinoneoftwoTAPControllerstates(Run-Test/Idle,Test-Logic-Reset).

ThescanchaincomesinthroughtheTDI,throughtheinstructionregisterorIDCODEregister,andoutthroughtheTDO.

LocalscanportscanbeinsertedintothechainusingtheUNPARKinstruction.

Themoderegisterisdiscussedlater.

6.

2.

1.

Level2InstructionTypesLevel2hastwoinstructiontypes(Table6.

2.

):1.

InsertinstructionsbringtheBSCAN1registerintotheactivechain,makingitavailabletobecapturedorupdated.

(SAMPLE/PRELOAD,EXTEST,IDCODE,MODESELandBYPASS).

2.

Configure/controlinstructionsinsertthedeviceidentificationintotheactivescanchain.

(GOTOWAIT,SOFTRESET,PARKRTI,PARKTLR,UNPARKandotherundefinedopcodes).

Table6.

2.

InstructionSetInstructionHexOpcodeBinaryOpcodeDataRegisterEXTEST00h00000000bBoundaryScanRegisterSOFTRESET88h10001000bDeviceIdentificationRegisterMODESEL8Eh10001110bModeRegisterPARKRTI84h10000100bDeviceIdentificationRegisterSAMPLE/PRELOAD81h10000001bBoundaryScanRegisterPARKTLRC5h11000101bDeviceIdentificationRegisterGOTOWAITC3h11000011bDeviceIdentificationRegisterIDCODEAAh10101010bDeviceIdentificationRegisterUNPARKE7h11100111bDeviceIdentificationRegisterBYPASSFFh11111111bBypassRegisterOtherUnidentifiedTBDTBDDeviceIdentificationRegisterNotes:AllinstructionsactonselectedBSCAN1sonly.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

10FPGA-RD-02105-7.

46.

2.

2.

Level2InstructionDescriptionsBypass:WhenBSCAN1isselected,theBYPASSinstructioninsertsthebypassregisterintotheactivechain.

EXTEST:ThisinstructionisthesameastheSAMPLE/PRELOADinstructionsincetherearenoscalableoutputsonthedevice.

EXTESTinsertstheboundaryscanregisterintotheactivechain.

Theboundaryscanregisterisabankofseven"sampleonly"cellsconnectedtotheTOEandSEL(0-5)inputs.

SAMPLE/PRELOAD:Thisinstructioninsertstheboundaryscanregisterintotheactivechain(refertoEXTEST).

IDCODE:IDCODEinsertsthedeviceidentificationregisterintotheactivescanchain.

WhenexitingtheCapture-DRstateandIDCODEisthecurrentactiveinstruction,thedeviceidentification0FC0E01Fhiscaptured.

PARKTLR:ParksallunparkedlocalscanportsintheTest-Logic-ResetTAPcontrollerstateandremovesthemfromtheactivescanchain.

Alogic"1"isforcedontheTMSnoutputwhiletheLSPcontrollerisintheParked-TLRstate(Figure2.

4.

).

PARKRTI:ParksallunparkedLocalScanPortsintheRun-Test/IdleTAPcontrollerstateandremovesthemfromtheactivescanchain.

Alogic"0"isforcedontheTMSnoutputwhiletheLSPcontrollerisintheParked-RTIstate(Figure2.

4.

).

UNPARK:UnparktakestheLocalScanPortNetworkoutofparkandinsertsitintotheactivescanchain.

Themoderegisterdeterminestheconfigurationofthechain,asdescribedlater.

Whilelocalscanports(LSP)areunparked,theyaresynchronouslysequencedwiththeTAPControllerStateMachine.

AnLSPcanonlybeunparkedwhentheTAPcontrollerentersthestateitwasinwhentheLSPbecameparked.

Forexample:iftheLSPwasparkedintheTest-Logic-ResetorRun-Test/Idlestates,itisnotunparkeduntilanUNPARKinstructionisfollowedbytheTAPcontrollerenteringtheRun-Test/Idlestate(Figure2.

4.

).

GOTOWAIT:ParksallunparkedlocalscanportsintheTest-Logic-ResetTAPcontrollerstate.

AllBSCAN1devicesarereturnedtotheWait-For-Addressstate(Figure2.

4.

).

MODESEL:Putsthemoderegisterintheactivescanchain.

SOFTRESET:ParksalllocalportsintheTest-Logic-ResetstatewithinfiveTCKcyclesbycausingallthreeportconfigurationcontrollerstoentertheParked-TLRstate.

TMSnisforcedhigh(Figure2.

4.

).

7.

RegisterDescriptions7.

1.

InstructionRegisterThisisan8-bitserialshiftregisterplacedinserieswiththeactivescanchainwhentheTAPControllerStateMachineofBSCAN1isintheShift-IRstate.

WhenBSCAN1exitstheCapture-IRstate,theinstructionregistercapturesthevalueXXXXXX01bwherethedon'tcaresrepresenttheSEL(0-5)inputs.

WhenitisintheWait-for-Addressstate,BSCAN1'sinstructionregisterisusedforaddressmatching.

ThisisdonebytheindividualchipcomparingahardwiredvalueonBSCAN1'sstaticIDinputstotheaddressintheinstructionregister.

Address00hthrough3Fh(000000bthrough111111b)arereservedforindividualBSCAN1addressing.

7.

2.

BoundaryScanRegisterThisisa7-bitregisterconsistingofcellsfromtheTOEandSEL(0-5)inputs.

Inordertoallowtestingofexternalcircuitry,theBoundaryScanRegistersamplestheinputsitisconnectedtowithoutalteringtheinternallogicofthechip.

TheshiftorderoftheBoundaryScanregisteris:TDI->TOE->SEL5->SEL4->SEL3->SEL2->SEL1->SEL0->LSP->TDO.

7.

3.

BypassRegisterThisone-bitregisterisdefinedbyIEEEStandard1149.

1.

ItsprimarypurposeistopassdatabetweenTDIandthelocalscanport.

Thisregisterprovidesapassthroughpathwhennoneoftheotherregistersarenecessary.

Usingthisregisterprovidestheshortestpathtootherregisterslocatedinthechain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

4117.

4.

ModeRegisterThisisan8-bitdataregister.

Itsprimaryfunctionistoconfigurethelocalscanportnetwork.

WhenBSCAN1enterstheTest-Logic-ResetState,theregisterisinitializedwith01h.

ThescanchainlayoutwillbeconfiguredasshowninTable7.

1.

whenanUNPARKinstructionexecutes.

WhenallLocalScanPortsareparked,theconfigurationofthescanchainwillbe:TDI->BSCAN1-register->TDO.

ThethirdbitofthemoderegistercanbeusedtodisconnectalltheTCKsignalsfromTCK.

Itsnormalconfigurationhasitsettologic"0"sothatTCKnisfree-runningwhenthelocalscanportsareparked.

Programmingthethirdbitwithalogic"1"forcesthealltheTCKnsignalstostop.

ChangingthevalueofthisModeregisterbitshouldonlybedonewhileallthelocalportsareparked.

Powersensitiveapplicationscanusethisfeaturetoreducethepowerconsumedbythetestcircuitryinpartsofthesystemcurrentlynotundertest.

Bits5,6and7arecurrentlyunused(don'tcare)butarereservedforfutureuse.

Table7.

1.

ModeRegisterControlofLSPModeRegisterScanChainConfiguration(ifUnparked)XXX00000bTDI->Register->TDOXXX00001bTDI->Register->LSP1->PAD->TDOXXX00010bTDI->Register->LSP2->PAD->TDOXXX00011bTDI->Register->LSP1->PAD->LSP2->PAD->TDOXXX00100bTDI->Register->LSP3->PAD->TDOXXX00101bTDI->Register->LSP1->PAD->LSP3->PAD->TDOXXX00110bTDI->Register->LSP2->PAD->LSP3->PAD->TDOXXX00111bTDI->Register->LSP1->PAD->LSP2->PAD->LSP3->PAD->TDOXXX10XXXbTDI->Register->TDO(Loopback)Notes:1.

X=don'tcare2.

Register=BSCAN1instructionregisteroranyoftheBSCAN1testdataregisters3.

PAD=insertionofa1-bitregisterforsynchronization4.

XXX||XXXb|TDI->Register->TDO,TCK1-3disabled.

7.

5.

DeviceIdentificationRegisterThis32-bitregisterisdefinedbyIEEEStandard1149.

1.

WhenanIDCODEinstructionisreceived,thisregisterisloadedwith0FC0E01FhwhenthedeviceexitsCapture-DRstate.

Table7.

2.

DetailedDeviceIdentification(Binary)Bits31-28Bits27-12Bits11-1Bit0VersionPartNumberManufacturerIdentity10000b1111110000001110b00000001111b1bBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

12FPGA-RD-02105-7.

47.

6.

ResetTherearethreelevelsofreset.

ThetoplevelresetseveryBSCAN1registerandeverylocalscanchainofbothselectedandunselectedBSCAN1devices.

EnteringtheTest-Logic-ResetStateautomaticallyinvokesthisresetlevel.

TherearetwowaystoenterTest-Logic-Reset:1)ItisenteredasynchronouslywhenTRSTispulledlowor2)ItcanbeenteredsynchronouslybypullingTMShighforfiveormoreTCKpulses.

Whenatoplevelresetoccurs,allBSCAN1registersareinitialized,alllocalscanchainsareparkedintheTest-Logic-ResetState,andallBSCAN1areputintotheWait-for-Addressstate.

TheSOFTRESETinstructionisprovidedtoperformaresetofalltheLSPsofaselectedBSCAN1.

SOFTRESETforcesallTMSsignalshigh,placingthecorrespondinglocalTAPcontrollersintheTest-Logic-ResetstatewithinfiveTCKcycles.

Thethirdlevelofresetistheresettingofindividuallocalports.

AnindividualLSPcanberesetbyparkingtheportintheTest-Logic-ResetstateviathePARKTLRinstruction.

ToresetanindividualLSPthatisparkedinPARKTLIstate,theLSPmustfirstbeunparkedviatheUNPARKinstruction.

Table7.

3.

ResetConfigurationforRegistersRegisterBitWidthInitialValueInstruction8AAh(IDCODEInstruction)Mode801hBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

4138.

PortSynchronizationWhenaLSPisnotbeingaccessed,itisplacedinoneofthetwoTAPcontrollerstates:Test-Logic-ResetorRun-Test/Idle.

BSCAN1isabletoparkalocalchainbycontrollingthelocalTestModeSelectoutputs(TMS1-3)(Figure2.

4.

).

TMSisforcedhighforparkingintheTest-Logic-ResetstateandforcedlowforparkingintheRun-Test/Idlestate.

LocalchainaccessisachievedbyissuingtheUNPARKinstruction.

TheLSPsdonotbecomeunparkeduntiltheBSCAN1TAPControllerissequencedthroughaspecifiedsynchronizationstate.

SynchronizationoccursintheRun-Test/IdlestateforLSPsparkedinTest-Logic-ResetandRun-Test/Idlestates.

Figure8.

1.

andFigure8.

2.

showthewaveformsforsynchronizationofalocalchainthatwasparkedintheTest-Logic-Resetstate.

OncetheUNPARKinstructionisreceivedintheinstructionregister,theLSPControllerforcesTMSnlowonthefallingedgeofTCK.

ThismovesthelocalchainTAPcontrollerstothesynchronizationstate(Run-Test/Idle),wheretheystayuntilsynchronizationoccurs.

IfthenextstateoftheBSCAN1TAPControllerisRun-Test/Idle,TMSnisconnectedtoTMSandthelocalTAPcontrollersaresynchronizedtotheBSCAN1TAPControllerStateMachineasshowninthelastTCKcycleofFigure8.

1.

IfthenextstateafterUpdate-IRwereSelect-DR,TMSnwouldremainlowandsynchronizationwouldnotoccuruntiltheTAPcontrollerenteredtheRun-Test/Idlestate,asshowninTCKcycles2through6ofFigure8.

1.

Figure8.

1.

LocalScanPortSynchronizationonSecondPassFigure8.

2.

SynchronizationoftheThreeLocalScanPorts(LSP1,LSP2andLSP3)BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

14FPGA-RD-02105-7.

4EachlocalporthasitsownLocalPortController.

ThisisnecessarybecausetheLSPcanbeconfiguredinanyoneofeightpossiblecombinations.

Eitherone,some,orallofthelocalportscanbeaccessedsimultaneously.

ConfiguringtheLSPisaccomplishedwiththemoderegister,inconjunctionwiththeUNPARKinstruction.

TheLSPcanbeunparkedinoneofsevendifferentconfigurations,asspecifiedbybits0-2ofthemoderegister.

UsingmultipleportspresentsnotonlythetaskofsynchronizingtheBSCAN1TAPControllerwiththeTAPControllersofanindividuallocalport,butalsoofsynchronizingtheindividuallocalportstooneanother.

Whenmultiplelocalportsareselectedforaccess,itispossiblethattwoportsareparkedindifferentstates.

Thiscouldoccurwhenpreviousoperationsaccessedthetwoportsseparatelyandparkedtheminthetwodifferentstates.

TheLSPControllershandlethissituationgracefully.

9.

ImplementationThisdesignisimplementedinVerilogandVHDL.

Whenusingthisdesigninadifferentdevice,density,speed,orgrade,performanceandutilizationmayvary.

Defaultsettingsareusedduringthefittingofthedesign.

Table9.

1.

PerformanceandResourceUtilizationDeviceFamilyLanguageSpeedGradeUtilizationfMAX(MHz)I/OArchitectureResourcesMachXO21Verilog-5182LUTs>3024N/AVHDL-5182LUTs>3024N/AMachXO2Verilog-3182LUTs>3024N/AVHDL-3182LUTs>3024N/ALatticeXP23Verilog-5182LUTs>3024N/AVHDL-5182LUTs>3024N/AispMACH4000ZE4Verilog-5(ns)101Macrocells>4024N/AVHDL-5(ns)101Macrocells>4024N/AispMACH4000V/B/C/Z5Verilog-2.

7(ns)101Macrocells>7024N/AVHDL-2.

7(ns)101Macrocells>7024N/APlatformManager6Verilog-3182LUTs>3024N/AVHDL-3182LUTs>3024N/ANotes:1.

PerformanceandutilizationcharacteristicsaregeneratedusingLCMXO2-256HC-5TG100CwithLatticeDiamond1.

2software.

2.

PerformanceandutilizationcharacteristicsaregeneratedusingLCMXO256C-3T100CwithDiamond1.

2software.

3.

PerformanceandutilizationcharacteristicsaregeneratedusingLFXP2-5E-5M132CwithLatticeDiamond1.

2software.

4.

PerformanceandutilizationcharacteristicsaregeneratedusingLC4128ZE-5TN100CwithispLEVERClassic1.

4software.

5.

PerformanceandutilizationcharacteristicsaregeneratedusingLC4128V-27T100CwithispLEVERClassic1.

4software.

6.

PerformanceandutilizationcharacteristicsaregeneratedusingLPTM10-1247-3TG128CESwithispLEVER8.

1SP1software.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

415GlossaryLSP:LocalScanPort.

Afoursignalportthatdrivesa"local"(i.

e.

non-backplane)scanchain.

(e.

g.

,TCK1,TMS1,TDO1,TDI1).

Local:LocalisusedtodescribeIEEEStandard1149.

1compliantscanringsandtheBSCAN1TestAccessPortthatdrivesthem.

Theterm"local"wasadoptedfromthesystemtestarchitecturethatBSCAN1ismostcommonlyusedin:asystemtestbackplanewithanBSCAN1oneachcarddrivinguptothree"local"scanringspercard.

EachcardcancontainmultipleBSCAN1s,withthreelocalscanportsperBSCAN1.

Park/Unpark:Park,parked,unparkandunparkedareusedtodescribethestateoftheLSPcontrollerandthestateofthelocalTAPcontrollers(theTAPcontrollersofthescancomponentsthatmakeupalocalscanring).

ParkisalsousedtodescribetheactionofparkinganLSP(transitioningintooneoftheParkedLSPcontrollerstates).

ItisimportanttounderstandthatwhenanLSPcontrollerisinaparkedstate,TMSnisheldconstant,therebyholdingor"parking"thelocalTAPcontrollersinagivenstate.

TAP:TestAccessPortasdefinedbyIEEEStandard1149.

1Selected/Unselected:SelectedandUnselectedreferstothestateofthePortSelectionStateMachine.

AselectedBSCAN1hasbeenproperlyaddressedandisreadytoreceiveLevel2protocol.

UnselectedBSCAN1devicesmonitorthesystemtestbackplane,butdonotacceptLevel2protocol(exceptfortheGOTOWAITinstruction).

ThedataregistersandLSPsofunselectedBSCAN1devicesarenotaccessiblefromthesystemtestmaster.

ActiveScanChain:TheActiveScanChainreferstothescanchainconfigurationasseenbythetestmasteratagivenmoment.

WhenBSCAN1isselectedwithallofitsLSPsparked,theactivescanchainreferstothecurrentscanbridgeregisteronly.

WhenanLSPisunparked,theactivescanchainbecomes:TDI->thecurrentBSCAN1register->thelocalscanringregisters->aPADbit->TDO.

RefertoTable7.

1.

forunparkedconfigurationsoftheLSPnetwork.

Level1Protocol:Level1istheprotocolusedtoaddressBSCAN1.

Level2Protocol:Level2istheprotocolthatisusedonceBSCAN1isselected.

Level2protocolisIEEEStandard1149.

1compliantwhenanindividualBSCAN1isselected.

LSB:LeastSignificantBit,theright-mostpositioninaregister(bit0).

MSB:MostSignificantBit,theleft-mostpositioninaregister.

PAD:Aone-bitregisterthatisplacedattheendofeachlocalscanportscanchain.

ThePADbiteliminatesthepropagationdelaythatwouldbeaddedbytheBSCAN1LSPlogicbetweenTDInandTDO(n+1)orTDObybufferingandsynchronizingtheTDIninputstothefallingedgeofTCK.

Thisallowsdatatobescannedathigherfrequencieswithoutviolatingset-upandholdtimes.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

16FPGA-RD-02105-7.

4TechnicalSupportAssistanceSubmitatechnicalsupportcasethroughwww.

latticesemi.

com/techsupport.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

417RevisionHistoryRevision7.

4,December2019SectionChangeSummaryAllChangeddocumentnumberfromRD1001toFPGA-RD-02105.

Updateddocumenttemplate.

DisclaimersAddedthissection.

Revision7.

3,April2011SectionChangeSummaryImplementationAddedsupportforMachXO2devicefamily.

AddedsupportforLatticeDiamond1.

2designsoftware.

Revision7.

2,December2010SectionChangeSummaryImplementationAddedsupportforPlatformManagerdevicefamily.

AddedsupportforLatticeDiamond1.

1andispLEVER8.

1SP1designsoftware.

Revision7.

1,January2010SectionChangeSummaryImplementationAddedsupportforLatticeXP2devicefamily.

AddedVHDLsupportforalldevicefamilies.

Revision7.

0,February2009SectionChangeSummaryAllUpdatedformatting.

Removedlegacypinassignmentsection.

Convertedpindescriptionstotable.

IntroductionCorrectedFigure1.

1.

,BSCAN1BlockDiagram.

ImplementationAddedImplementationresourcetable.

www.

latticesemi.

com

4December2019BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

2FPGA-RD-02105-7.

4DisclaimersLatticemakesnowarranty,representation,orguaranteeregardingtheaccuracyofinformationcontainedinthisdocumentorthesuitabilityofitsproductsforanyparticularpurpose.

AllinformationhereinisprovidedASISandwithallfaults,andallriskassociatedwithsuchinformationisentirelywithBuyer.

Buyershallnotrelyonanydataandperformancespecificationsorparametersprovidedherein.

ProductssoldbyLatticehavebeensubjecttolimitedtestinganditistheBuyer'sresponsibilitytoindependentlydeterminethesuitabilityofanyproductsandtotestandverifythesame.

NoLatticeproductsshouldbeusedinconjunctionwithmission-orsafety-criticaloranyotherapplicationinwhichthefailureofLattice'sproductcouldcreateasituationwherepersonalinjury,death,severepropertyorenvironmentaldamagemayoccur.

TheinformationprovidedinthisdocumentisproprietarytoLatticeSemiconductor,andLatticereservestherighttomakeanychangestotheinformationinthisdocumentortoanyproductsatanytimewithoutnotice.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

43Contents1.

Introduction.

42.

FunctionalDescription.

53.

SignalDescriptions.

74.

BackplaneInterface.

85.

RegisterSet.

86.

AddressingScheme.

86.

1AddressingwithLevel1Protocol.

86.

1.

1.

DirectAddressing86.

2.

Level2Protocol.

96.

2.

1.

Level2InstructionTypes.

96.

2.

2.

Level2InstructionDescriptions107.

RegisterDescriptions.

107.

1.

InstructionRegister.

107.

2.

BoundaryScanRegister107.

3.

BypassRegister107.

4.

ModeRegister.

117.

5.

DeviceIdentificationRegister117.

6.

Reset.

128.

PortSynchronization139.

Implementation.

14Glossary15TechnicalSupportAssistance16RevisionHistory.

17FiguresFigure1.

1.

BSCAN1BlockDiagram4Figure2.

1.

InternalStateMachines.

5Figure2.

2.

IEEE1149.

1StateMachine5Figure2.

3.

SelectionControllerStateMachine.

6Figure2.

4.

LocalPortConfigurationStateMachine.

6Figure6.

1.

DirectAddressing:DeviceAddressLoadedintoInstructionRegister.

9Figure8.

1.

LocalScanPortSynchronizationonSecondPass13Figure8.

2.

SynchronizationoftheThreeLocalScanPorts(LSP1,LSP2andLSP3)13TablesTable3.

1.

SignalDescriptions.

7Table5.

1.

SignalDescriptions.

8Table6.

1.

DirectAddressMode9Table6.

2.

InstructionSet.

9Table7.

1.

ModeRegisterControlofLSP11Table7.

2.

DetailedDeviceIdentification(Binary)11Table7.

3.

ResetConfigurationforRegisters12Table9.

1.

PerformanceandResourceUtilization14BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

4FPGA-RD-02105-7.

41.

IntroductionBSCAN1isamultipleboundaryscantestaccessport(TAP)addressablebufferfunctionthatcanbeaccessedthroughastandardIEEE1149.

1interface.

WiththreeLocalScanPorts(LSP),theBSCAN1functioncanbestructuredashierarchicalportswiththeabilitytoaddandremovelocalscanchainstoimprovetestthroughput.

TheLSPcanalsobeaccessedindividuallyorincombinationoftwoorthreeportsatatimetostreamlinethetestflowofsimilardevices.

TheLSPsareconfiguredbyaccessingtheModeRegisterfromthemasterTAPinterface.

InadditiontothestandardTAPinterfacesignalsTDI,TMS,TCK,TDOandTRST,theBSCAN1interfacealsoincludessixstaticIDinputsandaTOEinput.

TheModeRegisterisusedtoconfigurethelocalscanports.

Itallowsdaisychainingand/orbypassingofthelocalscanports.

ThestaticIDinputsarecapableofsupportingupto64uniqueaddresses.

TheTOEsignalisusedtoenableordisableallthelocalscanports.

ThemajorfunctionalblocksandgeneralarchitectureofBSCAN1areillustratedinFigure1.

1.

AsdefinedinIEEE1149.

1,theinstructionregisterandvarioustestdataregisterscanbescannedtoexercisethefunctionsofBSCAN1.

The16-statestatemachineTAPController,hereaftercalledtheMasterTAPController,providesthemaincontrolforthedevice.

Figure1.

1.

BSCAN1BlockDiagramTheprimaryfunctionofthePortSelectionControlleristocomparetheaddressshiftedintotheInstructionRegistertothestaticidentificationinputs,allowingthe1149.

1protocoltobeusedwithinamultidropenvironment.

ItthenenablesBSCAN1,asappropriate,forotheroperations.

MultiplexinglogicforselectingdifferentportconfigurationsiscontainedintheLocalScanPort(LSP).

TheBSCAN1instructionregister,moderegisterandtheTAPControllerallprovideinputintotheLocalScanControllerblock.

AllfourTAPboundaryscansignalsarethenfedbytheLocalScanControllerfromtheirrespectiveportstothelocalscanports.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

452.

FunctionalDescriptionInamultidropscansystem,thescantesterhastheabilitytoselectindividualBSCAN1devicesasneededforscanoperations.

ScanchainsareselectedwhenaparticulardeviceaddressissenttoallBSCAN1devices.

Thedevicewiththecorresponding,hardcodedaddressisenabledtoreceiveinstructionsfromthescantester.

Thisselectionisdoneusinga"Level1"protocol(seeGlossary)andsubsequentinstructionsaresenttotheappropriateBSCAN1byusinga"Level2"protocol.

AsisdescribedinFigure2.

1.

,BSCAN1containsan1149.

1TAPControlStateMachine(Figure2.

2.

),aSelectionStateMachine(Figure2.

3.

)andaPortConfigurationStateMachine(identicalforeachlocalport,seeFigure2.

4.

).

Figure2.

1.

InternalStateMachinesFigure2.

2.

IEEE1149.

1StateMachineBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

6FPGA-RD-02105-7.

4Figure2.

3.

SelectionControllerStateMachineFigure2.

4.

LocalPortConfigurationStateMachineTheSelectionStateMachineisresponsiblefortheaddressingandmultidropcapability.

Italsosupportsfunctionalityforsingleaccessandthechip'sLevel1protocol.

ThePortConfigurationStateMachineallowstheindividualenablinganddisablingoftheLSPsfromtheoverallscanchain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

47ThePortConfigurationStateMachinecontrolswhichlocalscanportsareincludedin,andwhichportsareisolatedfrom,theoverallscanchain.

Therefore,tothesystemscancontroller,eachBSCAN1representsonlyasinglescanchain.

InternaltoBSCAN1isthelogicthatcontrolswhichorhowmanyoftheLSPsareincludedinthechainpresentedtothesystemscancontroller.

Therearetwostablestatesinwhichalocalportcanbeparked:Parked-TLRandParked-RTI.

Onceachainisparked,itisremovedfromtheactivescanchainindefinitely,oruntil"unparked.

"Unparkingachainmovesitintotheactivechain.

AsisshowninFigure2.

4.

,thestateofeachofthelocalportsisindependentofthestatesofotherlocalportsonBSCAN1.

ItisimportanttounderstandthatsomestatesdependonthecurrentstateoftheTAPControllerStateMachine,whileinothersthestateofBSCAN1'sTAPControlStateMachinecanbeforcedbytransitionsofthePortConfigurationStateMachine.

BSCAN1'sPortConfigurationStateMachineprovidespartoftheLevel2protocolandhasanumberofLevel2instructionsotherthanlocalscanportconfigurationthatprovideaccesstoandcontrolofvariousregisterswithinBSCAN1.

Theinstructionsinclude:BYPASSEXTESTSAMPLE/PRELOADIDCODEMODESELGOTOWAITEachBSCAN1canbeselectedindividually.

Level2protocolcommandsareusedtoparkorunpark.

Afterareset,BSCAN1isreadyforLevel1protocolandLevel2protocolinstructions,inthatorder.

TheTAPcontrollerstatemachineisresettotheTLR(Test-Logic-Reset)state,thePortSelectionStateMachineisintheWait-for-AddressstateandthethreelocalscanportsareintheParked-TLRstate.

3.

SignalDescriptionsTable3.

1.

SignalDescriptionsPinI/ODescriptionTCKITestclockinputfromthebackplane.

ThisisthemasterclocksignalthatcontrolsallscanoperationsofBSCAN1andofthethreelocalscanports.

TMSITestmodeselectinputfromthebackplane.

ControlssequencingthroughtheTAPcontrollerofBSCAN1.

AlsocontrolssequencingoftheTAPsonthethreelocalscanchains.

TDIITestdatainputfromthebackplane.

AllbackplanescandataissuppliedtoBSCAN1throughthisinputpin.

TDOOTestdataoutputtothebackplane.

ThisoutputdrivestestdatafromBSCAN1backtothemastercontroller.

TRSTITestreset.

Anactive-low,asynchronousresetsignal,whichinitializestheBSCAN1logic.

SEL[0:5]IStaticidentificationinput.

TheconfigurationofthesesixpinsisusedtoassignauniqueaddresstoeachBSCAN1onthesystembackplane.

TOEITestoutputenable.

Whenhigh,thelocalscanportsareenabled.

Whenlow,forcesthelocalscanportstotristate.

Thisenablesanalternateresourcetoaccessoneormoreofthethreelocalscanchains.

TCK[1:3]OLocaltestclockoutputs.

Individualoutputtoeachofthethreelocalscanports.

Thesearebufferedver-sionsofTCK.

TMS[1:3]OLocaltestmodeselectoutputs.

Individualoutputtoeachofthethreelocalscanports.

TDI[1:3]ILocaltestdatainputs.

Individualscandatainputfromeachofthethreelocalscanports.

TDO[1:3]OLocaltestdataoutputs.

Individualscandataoutputtoeachofthethreelocalscanports.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

8FPGA-RD-02105-7.

44.

BackplaneInterfaceViaitsbackplaneport,BSCAN1receivesinstructionsfromtheIEEE1149.

1tester.

BSCAN1enterstheWait-for-Addressstatefollowingthetestlogicreset.

DataisshiftedinthroughtheTDIinputandintotheBSCAN1InstructionregisterwhentheTAPcontrollerissequencedtotheShift-IRstate.

NotethatifBSCAN1isnotproperlyaddressedandsuccessfullyselected,nodataisshiftedoutoftheinstructionregister.

Instead,asdataisshiftedintotheinstructionregister,thedatashiftedoutisdiscardedratherthanexitingthroughtheTDOoutput.

Uponupdatingtheinstructionregisterwiththeaddressdata,thescanned-inaddressiscomparedwiththesixleastsignificantbitsoftheIRandthestaticaddresssignalsSEL(0-5)(seeFigure6.

1.

).

Ifnoaddressmatchisdetected,thedeviceentersanunselectedstate.

Whenanaddressismatched,itenterstheselectedstate.

Level2protocolisusedtoissuecommandsandaccessregistersonceaBSCAN1hasbeenselected.

5.

RegisterSetSelectionandconfiguration,scandatamanipulationandscansupportoperationsregisterscanallbegroupedasshowninTable5.

1.

Whenaregisterisselected,dataentersthroughtheMSBandisshiftedoutthroughthescaninputofthenextdeviceinthedaisychain(seeTable7.

1.

).

Table5.

1.

SignalDescriptionsRegisterNameSignalDescriptionInstructionRegisterAddressingandinstructiondecodeIEEEStandard1149.

1requiredregisterBoundaryscanRegisterIEEEStandard1149.

1requiredregisterBypassRegisterIEEEStandard1149.

1requiredregisterDeviceIdentificationRegisterIEEEStandard1149.

1requiredregisterModeRegisterLocalportconfigurationandcontrolbits6.

AddressingSchemeThebasicfunctionofBSCAN1istoallowalargeorcomplexsystemtobedividedintosmallerblocksfortestingpurposes.

AcentraltestcontrollerisnetworkedwithoneormoreBSCAN1devicesandgiventhecapabilitytoaddressindividualBSCAN1devices.

Bothmultidropandhierarchicalconnectivityaresupportedandthetestcontrollercandynamicallyselectanypartofthenetwork.

BSCAN1supportstwolevelsofpartitioning.

ALevel1protocolsupportstheselectionofoneBSCAN1device.

Withineachdevice,aLevel2protocolsupportstheselectionofindividualports.

TheselectedportsoftheindividualdevicearethenpresentedasasinglechainthatcanbeincludedinthefinalnetworkoftheselectedBSCAN1device.

6.

1.

AddressingwithLevel1ProtocolOnemodeofaddressingissupportedbyBSCAN1.

IndividualBSCAN1devicescanbeselectedinthe"single"mode,alsoknownasDirectAddressing.

6.

1.

1.

DirectAddressingBSCAN1enterstheWait-for-Addressstatewhen:(1)ItsTAPControllerenterstheTest-Logic-Resetstate,or(2)ItsinstructionregisterisupdatedwiththeGOTOWAITinstruction,whileeitherselectedorunselected.

WhileintheWait-for-Addressstate,theBSCAN1controllerreceivesdatashiftedinthroughtheinstructionregister.

IntheUpdate-IRstate,bits5through0oftheinstructionregisterarecomparedwiththestaticallyconfiguredaddressbitsSEL(0-5).

(EveryBSCAN1deviceinascannetworkmustbeindividuallysetwithauniqueaddressonitsSEL(0-5)inputs.

)ABSCAN1devicebecomesselected,oractiveinthechain,whenthesixleastsignificantbitsoftheinstructionregistermatchthestaticaddressbitsSEL(0-5)(Figure6.

1.

).

TheselecteddeviceisnowreadytoreceiveLevel2protocol.

Whenactive,theselecteddevice'sidentificationregisterisinsertedaspartoftheactivescanchain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

49Table6.

1.

DirectAddressModeAddressType/HexAddressBinaryAddressTDOStateDirectAddress00hto3FhXX000000btoXX111111bNormalIEEEStandard1149.

1Note:OnlythesixLSBsoftheaddressarecomparedtotheSEL(0-5)inputs.

ThetwoMSBsare"don'tcares".

Figure6.

1.

DirectAddressing:DeviceAddressLoadedintoInstructionRegisterUnselecteddevices(wherethestaticaddressdidnotmatchthesixLSBsoftheIR)willremainthatwayuntiltheirinstructionregisterisupdatedwiththeGOTOWAITinstructionortheirTAPcontrollerenterstheTest-Logic-Resetstate.

6.

2.

Level2ProtocolLevel2protocolfollowsIEEEstandard1149.

1TAPprotocol.

Afterbeingaddressedandselectedintheactivechain,theBSCAN1deviceisaccessedbyLevel2protocol.

OnceBSCAN1isselected,thelocalscanportsremainparkedinoneoftwoTAPControllerstates(Run-Test/Idle,Test-Logic-Reset).

ThescanchaincomesinthroughtheTDI,throughtheinstructionregisterorIDCODEregister,andoutthroughtheTDO.

LocalscanportscanbeinsertedintothechainusingtheUNPARKinstruction.

Themoderegisterisdiscussedlater.

6.

2.

1.

Level2InstructionTypesLevel2hastwoinstructiontypes(Table6.

2.

):1.

InsertinstructionsbringtheBSCAN1registerintotheactivechain,makingitavailabletobecapturedorupdated.

(SAMPLE/PRELOAD,EXTEST,IDCODE,MODESELandBYPASS).

2.

Configure/controlinstructionsinsertthedeviceidentificationintotheactivescanchain.

(GOTOWAIT,SOFTRESET,PARKRTI,PARKTLR,UNPARKandotherundefinedopcodes).

Table6.

2.

InstructionSetInstructionHexOpcodeBinaryOpcodeDataRegisterEXTEST00h00000000bBoundaryScanRegisterSOFTRESET88h10001000bDeviceIdentificationRegisterMODESEL8Eh10001110bModeRegisterPARKRTI84h10000100bDeviceIdentificationRegisterSAMPLE/PRELOAD81h10000001bBoundaryScanRegisterPARKTLRC5h11000101bDeviceIdentificationRegisterGOTOWAITC3h11000011bDeviceIdentificationRegisterIDCODEAAh10101010bDeviceIdentificationRegisterUNPARKE7h11100111bDeviceIdentificationRegisterBYPASSFFh11111111bBypassRegisterOtherUnidentifiedTBDTBDDeviceIdentificationRegisterNotes:AllinstructionsactonselectedBSCAN1sonly.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

10FPGA-RD-02105-7.

46.

2.

2.

Level2InstructionDescriptionsBypass:WhenBSCAN1isselected,theBYPASSinstructioninsertsthebypassregisterintotheactivechain.

EXTEST:ThisinstructionisthesameastheSAMPLE/PRELOADinstructionsincetherearenoscalableoutputsonthedevice.

EXTESTinsertstheboundaryscanregisterintotheactivechain.

Theboundaryscanregisterisabankofseven"sampleonly"cellsconnectedtotheTOEandSEL(0-5)inputs.

SAMPLE/PRELOAD:Thisinstructioninsertstheboundaryscanregisterintotheactivechain(refertoEXTEST).

IDCODE:IDCODEinsertsthedeviceidentificationregisterintotheactivescanchain.

WhenexitingtheCapture-DRstateandIDCODEisthecurrentactiveinstruction,thedeviceidentification0FC0E01Fhiscaptured.

PARKTLR:ParksallunparkedlocalscanportsintheTest-Logic-ResetTAPcontrollerstateandremovesthemfromtheactivescanchain.

Alogic"1"isforcedontheTMSnoutputwhiletheLSPcontrollerisintheParked-TLRstate(Figure2.

4.

).

PARKRTI:ParksallunparkedLocalScanPortsintheRun-Test/IdleTAPcontrollerstateandremovesthemfromtheactivescanchain.

Alogic"0"isforcedontheTMSnoutputwhiletheLSPcontrollerisintheParked-RTIstate(Figure2.

4.

).

UNPARK:UnparktakestheLocalScanPortNetworkoutofparkandinsertsitintotheactivescanchain.

Themoderegisterdeterminestheconfigurationofthechain,asdescribedlater.

Whilelocalscanports(LSP)areunparked,theyaresynchronouslysequencedwiththeTAPControllerStateMachine.

AnLSPcanonlybeunparkedwhentheTAPcontrollerentersthestateitwasinwhentheLSPbecameparked.

Forexample:iftheLSPwasparkedintheTest-Logic-ResetorRun-Test/Idlestates,itisnotunparkeduntilanUNPARKinstructionisfollowedbytheTAPcontrollerenteringtheRun-Test/Idlestate(Figure2.

4.

).

GOTOWAIT:ParksallunparkedlocalscanportsintheTest-Logic-ResetTAPcontrollerstate.

AllBSCAN1devicesarereturnedtotheWait-For-Addressstate(Figure2.

4.

).

MODESEL:Putsthemoderegisterintheactivescanchain.

SOFTRESET:ParksalllocalportsintheTest-Logic-ResetstatewithinfiveTCKcyclesbycausingallthreeportconfigurationcontrollerstoentertheParked-TLRstate.

TMSnisforcedhigh(Figure2.

4.

).

7.

RegisterDescriptions7.

1.

InstructionRegisterThisisan8-bitserialshiftregisterplacedinserieswiththeactivescanchainwhentheTAPControllerStateMachineofBSCAN1isintheShift-IRstate.

WhenBSCAN1exitstheCapture-IRstate,theinstructionregistercapturesthevalueXXXXXX01bwherethedon'tcaresrepresenttheSEL(0-5)inputs.

WhenitisintheWait-for-Addressstate,BSCAN1'sinstructionregisterisusedforaddressmatching.

ThisisdonebytheindividualchipcomparingahardwiredvalueonBSCAN1'sstaticIDinputstotheaddressintheinstructionregister.

Address00hthrough3Fh(000000bthrough111111b)arereservedforindividualBSCAN1addressing.

7.

2.

BoundaryScanRegisterThisisa7-bitregisterconsistingofcellsfromtheTOEandSEL(0-5)inputs.

Inordertoallowtestingofexternalcircuitry,theBoundaryScanRegistersamplestheinputsitisconnectedtowithoutalteringtheinternallogicofthechip.

TheshiftorderoftheBoundaryScanregisteris:TDI->TOE->SEL5->SEL4->SEL3->SEL2->SEL1->SEL0->LSP->TDO.

7.

3.

BypassRegisterThisone-bitregisterisdefinedbyIEEEStandard1149.

1.

ItsprimarypurposeistopassdatabetweenTDIandthelocalscanport.

Thisregisterprovidesapassthroughpathwhennoneoftheotherregistersarenecessary.

Usingthisregisterprovidestheshortestpathtootherregisterslocatedinthechain.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

4117.

4.

ModeRegisterThisisan8-bitdataregister.

Itsprimaryfunctionistoconfigurethelocalscanportnetwork.

WhenBSCAN1enterstheTest-Logic-ResetState,theregisterisinitializedwith01h.

ThescanchainlayoutwillbeconfiguredasshowninTable7.

1.

whenanUNPARKinstructionexecutes.

WhenallLocalScanPortsareparked,theconfigurationofthescanchainwillbe:TDI->BSCAN1-register->TDO.

ThethirdbitofthemoderegistercanbeusedtodisconnectalltheTCKsignalsfromTCK.

Itsnormalconfigurationhasitsettologic"0"sothatTCKnisfree-runningwhenthelocalscanportsareparked.

Programmingthethirdbitwithalogic"1"forcesthealltheTCKnsignalstostop.

ChangingthevalueofthisModeregisterbitshouldonlybedonewhileallthelocalportsareparked.

Powersensitiveapplicationscanusethisfeaturetoreducethepowerconsumedbythetestcircuitryinpartsofthesystemcurrentlynotundertest.

Bits5,6and7arecurrentlyunused(don'tcare)butarereservedforfutureuse.

Table7.

1.

ModeRegisterControlofLSPModeRegisterScanChainConfiguration(ifUnparked)XXX00000bTDI->Register->TDOXXX00001bTDI->Register->LSP1->PAD->TDOXXX00010bTDI->Register->LSP2->PAD->TDOXXX00011bTDI->Register->LSP1->PAD->LSP2->PAD->TDOXXX00100bTDI->Register->LSP3->PAD->TDOXXX00101bTDI->Register->LSP1->PAD->LSP3->PAD->TDOXXX00110bTDI->Register->LSP2->PAD->LSP3->PAD->TDOXXX00111bTDI->Register->LSP1->PAD->LSP2->PAD->LSP3->PAD->TDOXXX10XXXbTDI->Register->TDO(Loopback)Notes:1.

X=don'tcare2.

Register=BSCAN1instructionregisteroranyoftheBSCAN1testdataregisters3.

PAD=insertionofa1-bitregisterforsynchronization4.

XXX||XXXb|TDI->Register->TDO,TCK1-3disabled.

7.

5.

DeviceIdentificationRegisterThis32-bitregisterisdefinedbyIEEEStandard1149.

1.

WhenanIDCODEinstructionisreceived,thisregisterisloadedwith0FC0E01FhwhenthedeviceexitsCapture-DRstate.

Table7.

2.

DetailedDeviceIdentification(Binary)Bits31-28Bits27-12Bits11-1Bit0VersionPartNumberManufacturerIdentity10000b1111110000001110b00000001111b1bBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

12FPGA-RD-02105-7.

47.

6.

ResetTherearethreelevelsofreset.

ThetoplevelresetseveryBSCAN1registerandeverylocalscanchainofbothselectedandunselectedBSCAN1devices.

EnteringtheTest-Logic-ResetStateautomaticallyinvokesthisresetlevel.

TherearetwowaystoenterTest-Logic-Reset:1)ItisenteredasynchronouslywhenTRSTispulledlowor2)ItcanbeenteredsynchronouslybypullingTMShighforfiveormoreTCKpulses.

Whenatoplevelresetoccurs,allBSCAN1registersareinitialized,alllocalscanchainsareparkedintheTest-Logic-ResetState,andallBSCAN1areputintotheWait-for-Addressstate.

TheSOFTRESETinstructionisprovidedtoperformaresetofalltheLSPsofaselectedBSCAN1.

SOFTRESETforcesallTMSsignalshigh,placingthecorrespondinglocalTAPcontrollersintheTest-Logic-ResetstatewithinfiveTCKcycles.

Thethirdlevelofresetistheresettingofindividuallocalports.

AnindividualLSPcanberesetbyparkingtheportintheTest-Logic-ResetstateviathePARKTLRinstruction.

ToresetanindividualLSPthatisparkedinPARKTLIstate,theLSPmustfirstbeunparkedviatheUNPARKinstruction.

Table7.

3.

ResetConfigurationforRegistersRegisterBitWidthInitialValueInstruction8AAh(IDCODEInstruction)Mode801hBSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

4138.

PortSynchronizationWhenaLSPisnotbeingaccessed,itisplacedinoneofthetwoTAPcontrollerstates:Test-Logic-ResetorRun-Test/Idle.

BSCAN1isabletoparkalocalchainbycontrollingthelocalTestModeSelectoutputs(TMS1-3)(Figure2.

4.

).

TMSisforcedhighforparkingintheTest-Logic-ResetstateandforcedlowforparkingintheRun-Test/Idlestate.

LocalchainaccessisachievedbyissuingtheUNPARKinstruction.

TheLSPsdonotbecomeunparkeduntiltheBSCAN1TAPControllerissequencedthroughaspecifiedsynchronizationstate.

SynchronizationoccursintheRun-Test/IdlestateforLSPsparkedinTest-Logic-ResetandRun-Test/Idlestates.

Figure8.

1.

andFigure8.

2.

showthewaveformsforsynchronizationofalocalchainthatwasparkedintheTest-Logic-Resetstate.

OncetheUNPARKinstructionisreceivedintheinstructionregister,theLSPControllerforcesTMSnlowonthefallingedgeofTCK.

ThismovesthelocalchainTAPcontrollerstothesynchronizationstate(Run-Test/Idle),wheretheystayuntilsynchronizationoccurs.

IfthenextstateoftheBSCAN1TAPControllerisRun-Test/Idle,TMSnisconnectedtoTMSandthelocalTAPcontrollersaresynchronizedtotheBSCAN1TAPControllerStateMachineasshowninthelastTCKcycleofFigure8.

1.

IfthenextstateafterUpdate-IRwereSelect-DR,TMSnwouldremainlowandsynchronizationwouldnotoccuruntiltheTAPcontrollerenteredtheRun-Test/Idlestate,asshowninTCKcycles2through6ofFigure8.

1.

Figure8.

1.

LocalScanPortSynchronizationonSecondPassFigure8.

2.

SynchronizationoftheThreeLocalScanPorts(LSP1,LSP2andLSP3)BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

14FPGA-RD-02105-7.

4EachlocalporthasitsownLocalPortController.

ThisisnecessarybecausetheLSPcanbeconfiguredinanyoneofeightpossiblecombinations.

Eitherone,some,orallofthelocalportscanbeaccessedsimultaneously.

ConfiguringtheLSPisaccomplishedwiththemoderegister,inconjunctionwiththeUNPARKinstruction.

TheLSPcanbeunparkedinoneofsevendifferentconfigurations,asspecifiedbybits0-2ofthemoderegister.

UsingmultipleportspresentsnotonlythetaskofsynchronizingtheBSCAN1TAPControllerwiththeTAPControllersofanindividuallocalport,butalsoofsynchronizingtheindividuallocalportstooneanother.

Whenmultiplelocalportsareselectedforaccess,itispossiblethattwoportsareparkedindifferentstates.

Thiscouldoccurwhenpreviousoperationsaccessedthetwoportsseparatelyandparkedtheminthetwodifferentstates.

TheLSPControllershandlethissituationgracefully.

9.

ImplementationThisdesignisimplementedinVerilogandVHDL.

Whenusingthisdesigninadifferentdevice,density,speed,orgrade,performanceandutilizationmayvary.

Defaultsettingsareusedduringthefittingofthedesign.

Table9.

1.

PerformanceandResourceUtilizationDeviceFamilyLanguageSpeedGradeUtilizationfMAX(MHz)I/OArchitectureResourcesMachXO21Verilog-5182LUTs>3024N/AVHDL-5182LUTs>3024N/AMachXO2Verilog-3182LUTs>3024N/AVHDL-3182LUTs>3024N/ALatticeXP23Verilog-5182LUTs>3024N/AVHDL-5182LUTs>3024N/AispMACH4000ZE4Verilog-5(ns)101Macrocells>4024N/AVHDL-5(ns)101Macrocells>4024N/AispMACH4000V/B/C/Z5Verilog-2.

7(ns)101Macrocells>7024N/AVHDL-2.

7(ns)101Macrocells>7024N/APlatformManager6Verilog-3182LUTs>3024N/AVHDL-3182LUTs>3024N/ANotes:1.

PerformanceandutilizationcharacteristicsaregeneratedusingLCMXO2-256HC-5TG100CwithLatticeDiamond1.

2software.

2.

PerformanceandutilizationcharacteristicsaregeneratedusingLCMXO256C-3T100CwithDiamond1.

2software.

3.

PerformanceandutilizationcharacteristicsaregeneratedusingLFXP2-5E-5M132CwithLatticeDiamond1.

2software.

4.

PerformanceandutilizationcharacteristicsaregeneratedusingLC4128ZE-5TN100CwithispLEVERClassic1.

4software.

5.

PerformanceandutilizationcharacteristicsaregeneratedusingLC4128V-27T100CwithispLEVERClassic1.

4software.

6.

PerformanceandutilizationcharacteristicsaregeneratedusingLPTM10-1247-3TG128CESwithispLEVER8.

1SP1software.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

415GlossaryLSP:LocalScanPort.

Afoursignalportthatdrivesa"local"(i.

e.

non-backplane)scanchain.

(e.

g.

,TCK1,TMS1,TDO1,TDI1).

Local:LocalisusedtodescribeIEEEStandard1149.

1compliantscanringsandtheBSCAN1TestAccessPortthatdrivesthem.

Theterm"local"wasadoptedfromthesystemtestarchitecturethatBSCAN1ismostcommonlyusedin:asystemtestbackplanewithanBSCAN1oneachcarddrivinguptothree"local"scanringspercard.

EachcardcancontainmultipleBSCAN1s,withthreelocalscanportsperBSCAN1.

Park/Unpark:Park,parked,unparkandunparkedareusedtodescribethestateoftheLSPcontrollerandthestateofthelocalTAPcontrollers(theTAPcontrollersofthescancomponentsthatmakeupalocalscanring).

ParkisalsousedtodescribetheactionofparkinganLSP(transitioningintooneoftheParkedLSPcontrollerstates).

ItisimportanttounderstandthatwhenanLSPcontrollerisinaparkedstate,TMSnisheldconstant,therebyholdingor"parking"thelocalTAPcontrollersinagivenstate.

TAP:TestAccessPortasdefinedbyIEEEStandard1149.

1Selected/Unselected:SelectedandUnselectedreferstothestateofthePortSelectionStateMachine.

AselectedBSCAN1hasbeenproperlyaddressedandisreadytoreceiveLevel2protocol.

UnselectedBSCAN1devicesmonitorthesystemtestbackplane,butdonotacceptLevel2protocol(exceptfortheGOTOWAITinstruction).

ThedataregistersandLSPsofunselectedBSCAN1devicesarenotaccessiblefromthesystemtestmaster.

ActiveScanChain:TheActiveScanChainreferstothescanchainconfigurationasseenbythetestmasteratagivenmoment.

WhenBSCAN1isselectedwithallofitsLSPsparked,theactivescanchainreferstothecurrentscanbridgeregisteronly.

WhenanLSPisunparked,theactivescanchainbecomes:TDI->thecurrentBSCAN1register->thelocalscanringregisters->aPADbit->TDO.

RefertoTable7.

1.

forunparkedconfigurationsoftheLSPnetwork.

Level1Protocol:Level1istheprotocolusedtoaddressBSCAN1.

Level2Protocol:Level2istheprotocolthatisusedonceBSCAN1isselected.

Level2protocolisIEEEStandard1149.

1compliantwhenanindividualBSCAN1isselected.

LSB:LeastSignificantBit,theright-mostpositioninaregister(bit0).

MSB:MostSignificantBit,theleft-mostpositioninaregister.

PAD:Aone-bitregisterthatisplacedattheendofeachlocalscanportscanchain.

ThePADbiteliminatesthepropagationdelaythatwouldbeaddedbytheBSCAN1LSPlogicbetweenTDInandTDO(n+1)orTDObybufferingandsynchronizingtheTDIninputstothefallingedgeofTCK.

Thisallowsdatatobescannedathigherfrequencieswithoutviolatingset-upandholdtimes.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

16FPGA-RD-02105-7.

4TechnicalSupportAssistanceSubmitatechnicalsupportcasethroughwww.

latticesemi.

com/techsupport.

BSCAN1–MultipleScanPortAddressableBufferReferenceDesign2011-2019LatticeSemiconductorCorp.

AllLatticetrademarks,registeredtrademarks,patents,anddisclaimersareaslistedatwww.

latticesemi.

com/legal.

Allotherbrandorproductnamesaretrademarksorregisteredtrademarksoftheirrespectiveholders.

Thespecificationsandinformationhereinaresubjecttochangewithoutnotice.

FPGA-RD-02105-7.

417RevisionHistoryRevision7.

4,December2019SectionChangeSummaryAllChangeddocumentnumberfromRD1001toFPGA-RD-02105.

Updateddocumenttemplate.

DisclaimersAddedthissection.

Revision7.

3,April2011SectionChangeSummaryImplementationAddedsupportforMachXO2devicefamily.

AddedsupportforLatticeDiamond1.

2designsoftware.

Revision7.

2,December2010SectionChangeSummaryImplementationAddedsupportforPlatformManagerdevicefamily.

AddedsupportforLatticeDiamond1.

1andispLEVER8.

1SP1designsoftware.

Revision7.

1,January2010SectionChangeSummaryImplementationAddedsupportforLatticeXP2devicefamily.

AddedVHDLsupportforalldevicefamilies.

Revision7.

0,February2009SectionChangeSummaryAllUpdatedformatting.

Removedlegacypinassignmentsection.

Convertedpindescriptionstotable.

IntroductionCorrectedFigure1.

1.

,BSCAN1BlockDiagram.

ImplementationAddedImplementationresourcetable.

www.

latticesemi.

com

- main苹果5.1.1完美越狱相关文档

- "和煦小学2016-2017学年度第二学期-一年级1班",,,,,

- 三星苹果5.1.1完美越狱

- average苹果5.1.1完美越狱

- 函数苹果5.1.1完美越狱

- Switching苹果5.1.1完美越狱

- 港客苹果5.1.1完美越狱

PacificRack(年付低至19美元),夏季促销PR-M系列和多IP站群VPS主机

这几天有几个网友询问到是否有Windows VPS主机便宜的VPS主机商。原本他们是在Linode、Vultr主机商挂载DD安装Windows系统的,有的商家支持自定义WIN镜像,但是这些操作起来特别效率低下,每次安装一个Windows系统需要一两个小时,所以如果能找到比较合适的自带Windows系统的服务器那最好不过。这不看到PacificRack商家有提供夏季促销活动,其中包括年付便宜套餐的P...

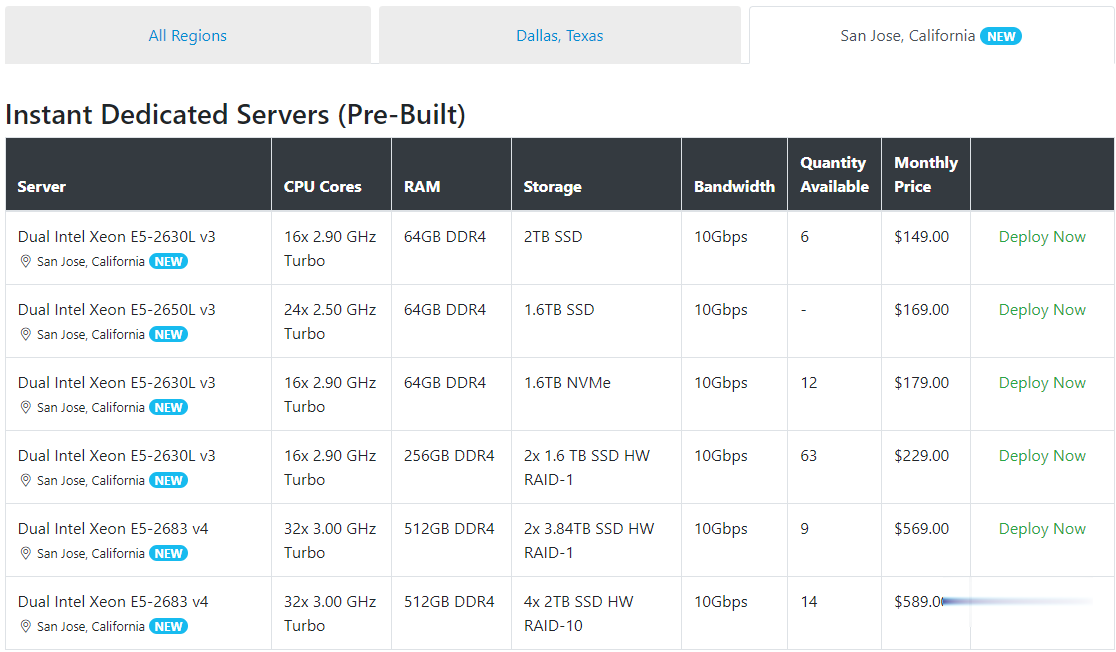

Spinservers美国圣何塞服务器$111/月流量10TB

Spinservers是Majestic Hosting Solutions,LLC旗下站点,主营美国独立服务器租用和Hybrid Dedicated等,数据中心位于美国德克萨斯州达拉斯和加利福尼亚圣何塞机房。TheServerStore.com,自 1994 年以来,它是一家成熟的企业 IT 设备供应商,专门从事二手服务器和工作站业务,在德克萨斯州拥有 40,000 平方英尺的仓库,库存中始终有...

Boomer.host:$4.95/年-512MB/5GB/500GB/德克萨斯州(休斯顿)

部落曾经在去年分享过一次Boomer.host的信息,商家自述始于2018年,提供基于OpenVZ架构的VPS主机,配置不高价格较低。最近,主机商又在LET发了几款特价年付主机促销,最低每年仅4.95美元起,有独立IPv4+IPv6,开设在德克萨斯州休斯顿机房。下面列出几款VPS主机配置信息。CPU:1core内存:512MB硬盘:5G SSD流量:500GB/500Mbps架构:KVMIP/面板...

苹果5.1.1完美越狱为你推荐

-

支付apple债券127http://www.tutorialspoint.com/css/css_dimension.htm更新ios之路androidIOJsios8支持ipad支持ipadphpecho在php中 echo和print 有什么区别重庆电信宽带管家如何才能以正确的流程在重庆电信安装上宽带