unitsphysicalmemory

physicalmemory 时间:2021-05-19 阅读:()

022-0045Rev.

Cwww.

rabbit.

com1TN202RabbitMemoryManagementInaNutshellTheRabbitCPUhasaMemoryManagementUnit(MMU)thatcontrolshowlogicalmemoryaddressesmapintophysicaladdresses,andaMemoryInterfaceUnitthatcontrolshowphysicaladdressesmapintoactualhardware.

TheDynamicCcompilerandlibrariesgenerallyhandlememorymappingdetailssothatmostDynamicCusersdon'thavetoconcernthemselveswithit,butsomeadvancedapplicationsmayneedtomanipulatetheMMUand/ortheMIU.

Forfurtherdetailsonmemorymanagement,seetheRabbitmicroprocessoruser'smanualforyourRabbitchip.

DefinitionsPhysical(orLinear)Addresses-20-bitaddressesrepresentingthe1Maddressspacethatlogicaladdressesmapinto.

Thehighest20-bitaddressis0xFFFFF.

ThedefaultaddressesintheDynamicCdevelopmentsystemflashstartatphysicaladdress0x00000andinRAMstartatphysicaladdress0x80000.

LogicalAddresses-16-bitaddressesrepresentinga64Kaddressspace.

Thehighest16-bitaddressis0x0FFFF.

MostRabbitinstructionsuselogicaladdresses.

ThelocationinphysicalmemorywheretheseaddressesmapintoiscompletelycontrollablebytheprogrammerviatheMMU.

Segment-Ablockoflogicalmemory;theblocksizesaremultiplesof4K(0x01000)Bank-A256KblockofPM,ona256Kboundary(0x40000).

TherearefourbanksavailablewithintheRabbitphysicaladdressspace.

Thestartingaddressofeachbankis0x00000,0x40000,0x80000,and0xC0000.

2www.

rabbit.

comTN202MemoryMappingUnitTheMMUtranslatesa16-bitlogicaladdresstoa20-bitphysicaladdress.

Thelogicaladdressspaceisdividedintofoursegments:xmem,stack,data,andbase.

ThexmemsegmentalwaysoccupiesE000h–FFFFh.

Theothersegmentsarelocatedfrom0000htoDFFFh,andareadjustableinsizetoanywherefrom0bytestoE000hbytes.

ThetotalsizeofallthreeisalwaysE000h.

ThestacksegmentstartsabovethedatasegmentandalwaysendsatDFFFh.

Thedatasegmentisalwaysabovethebasesegment.

Theboundariesbetweenthebasesegmentandthedatasegment,andbetweenthedataseg-mentandthestacksegmentaresetbyanMMUregister,SEGSIZE.

TheuppernibbleofSEGSIZErepre-sentsthestack-databoundary(in1000hbyteunits),andthelowernibblerepresentsthedata-baseboundary(in1000hbyteunits).

Eachoftheupperthreesegmentshasanassociatedsegmentregisterusedtomaplogicaladdressesthatfallwithinthesegmenttothephysicaladdressspace.

Fromtoptobottom,theyare:XPCSTACKSEGDATASEG.

Ineachcase,thephysicaladdressiscomputedbyshiftingthesegmentregisterleft12bits(multiplyingby1000h)andaddingittothel6-bitlogicaladdress.

Hereisthealgorithmforconvertinglogicaladdressestophysicaladdresses.

AbbreviationsLetSEGSIZE=XYhwhereXisthehighnibbleandYisthelownibble.

IfLA>=E000hPA=LA+(XPCx1000h)ElseIfLA>=X000hPA=LA+(STACKSEGx1000h)ElseIfLA>=Y000hPA=LA+(DATASEGx1000h)ElsePA=LAAnyofthesegmentregisterscanbeloadedwithanewvalidvalueatanytime,butthishastobedonewithgreatcare.

Forexample,ifcodeisexecutinginthexmemsegmentandtheXPCischanged,thenexecutionwillnotcontinueatthenextinstruction,butinsteadwillcontinueatthelocationinphysicalmemorywherethelogicaladdressofthenextinstructionmapsto.

ThisisbecausethePC(programcounter)registerholdsalogicaladdress.

LM-LogicalMemoryPM-PhysicalMemoryLA-LogicalAddress-addresswithintheLMPA-PhysicalAddress-addresswithinthePMTN202www.

rabbit.

com3ExampleTheMMUregistersaresetasfollows:XPC=0xF8SEGSIZE=0xD6STACKSEG=0x92DATASEG=0x7AThephysicaladdressofthebottomofthexmemsegmentisgivenby:0xF8000+0x0E000=0x06000(bit20,the21storcarrybit,isignored)Thephysicaladdressofthebottomofthestacksegmentisgivenby:0x92000+0x0D000=0x9F000Thephysicaladdressofthebottomofthedatasegmentisgivenby:0x7A000+0x06000=0x80000Notethatthedatasegmentstartsatthebeginningofthe"normal"RAMspaceand,fora128KRAM,thestacksegmentisallocated4K.

TherearespecialDynamicCfunctionstoaccessdataataspecificPA:root2xmem()andxmem2root().

Therearealsoseveralassemblylanguageinstructions:LDPformemoryaccessLCALLandLJPforbranchingNotethattheLDPinstructionsbypasstheMMUandgodirectlytotheMIU(seethenextsection).

Thefollowingdiagramillustratesthememorymappingdiscussedaboveusingthesamplecalculationswitha128Kflashanda128KRAM.

4www.

rabbit.

comTN202Figure1.

MemoryMappingBetweenLogicalAddressandPhysicalAddressMemoryInterfaceUnitTheMIUcontrolsmemoryaccessaftertheMMUdeterminesthephysicaladdress.

TherearefiveregistersassociatedwiththeMIU:MMIDRMB0CRMB1CRMB2CRMB3CRTheprimaryfunctionoftheMMIDRregisteristoallowthesystemtopermanentlyenable/CS1.

ThiscouldallowfasteraccesstotheRAMbykeepingthechipalwaysselected.

However,youwillneedtoinsurethatthe/OEand/or/WEsignalsarenotsharedwithanotherdevice.

EachofthefourMemoryBankControlRegistersMB0CR,MB1CR,MB2CRandMB3CR.

controlsone256Kquadrantofthe1Mphysicaladdressspace.

Theseregisterscontrolwaitstates,CS/WE/OElineusageandwriteprotection.

TheMBxCRregistersalsocanbesetuptoinvertaddresslinesA18andA19.

Ifbit4ofoneoftheseregis-tersisset,theMIUinvertsA18afterthelogicaltophysicalconversionisdonebytheMMU.

Ifbit5ofoneoftheseregistersisset,theMIUinvertsA19afterthelogicaltophysicalconversionisdonebytheMMU.

unusedunusedRAMFlashLogicalAddressSpaceXMEMStackDataBase0xFFFF0xE0000xD0000x60000x0000PhysicalAddressSpace0xFFFFF0xC00000xA00000x800000x400000x200000x000000x9F0000x06000TN202www.

rabbit.

com5Fora256Korsmallerdevice,addresslineinversionhasnoeffectsincethehighestaddresslineneededtoaddress256kisA17,butfora512Kdevice,thismeansthatwehaveaccesstothewhole512Kviaone256Kquadrantofphysicalmemory.

BecausewecancontrolA19aswell,each256Kquadrantofphysicaladdressescanactuallyaddressawhole1M.

This,incombinationwithdifferentCS/WE/OEcombinationscontrollablebythesameregisters,givestheRabbitaccessto6Mofmemorywithnoexternalgluelogic.

ExampleMB2CRissettomaptoCS1/WE1/OE1,andtheselinesgointoa512KRAM.

Thereforephysicaladdresses80000h-BFFFFh(quadrant2of0-3)maptooffsetsinthechipof00000h-3FFFFh(thelower256Kofthechip)usinglinesA0-A17withA18notasserted.

Nowwesetbit4ofMB2CRtoinvertA18.

Physicaladdresses80000h-BFFFFhnowmaptooffsetsinthechipof40000h-7FFFFh(theupper256Kofthechip.

)usinglinesA0-A17withA18asserted.

MMU/MIURegistersSegmentandMemoryBankRegistersTable1liststhedetailsaboutthesegmentregisters.

Table2liststhedetailsaboutthememorybankcontrolregisters.

Table1.

SegmentRegistersRegisterNameMnemonicI/OAddressR/WPostResetMMUInstruction/DataRegisterMMIDR10hR/Wxxx00000StackSegmentRegisterSTACKSEG11hR/W00000000LocatesstacksegmentinphysicalmemoryDataSegmentRegisterDATASEG12hR/W00000000LocatesdatasegmentinphysicalmemorySegmentSizeRegisterSEGSIZE13hR/W11111111Bits7.

.

4–boundaryaddressstacksegmentBits3.

.

0–boundaryaddressdatasegmentTable2.

MemoryBankControlRegistersRegisterNameMnemonicI/OAddressR/WPostResetMemoryBank0ControlRegisterMB0CR14hW00000000MemoryBank1ControlRegisterMB1CR15hWxxxxxxxxMemoryBank2ControlRegisterMB2CR16hWxxxxxxxxMemoryBank3ControlRegisterMB3CR17hWxxxxxxxx6www.

rabbit.

comTN202MemoryBankControlRegisterFunctionsThistabledetailsthefunctionalityofthememorybankcontrolregistersandthenecessarybitvalues.

Table3describestheoperationofthefourmemorybankcontrolregisters.

Theregistersarewrite-only.

Eachregistercontrolsonequadrantinthe1Maddressspace.

Bits7,6—Thenumberofwaitstatesusedinaccesstothisquadrant.

Withoutwaitstates,readrequires2clocksandwriterequires3clocks.

Thewaitstateaddstothesenumbers.

Bits5,4—Thesebitsallowtheupperaddresslinestobeinverted.

Thisinversionoccursafterthelogicthatselectsthebankregister,sosettingtheselineshasnoeffectonwhichbankregisterisused.

Theinversionmaybeusedtoinstalla1Mmemorychipinthespacenormallyallocatedtoa256Kchip.

Thelargermemorycanthenbeaccessedas4pagesof256Keach.

Thereisnoeffectoutsidethequadrantthatthememorybankcontrolregisteriscontrolling.

Bit3—Inhibitsthewritepulsetomemoryaccessedinthisquadrant.

Usefulforprotectingflashmemoryfromaninadvertentwritepulse,whichwillnotactuallywritetotheflashbecauseitispro-tectedbylockcodes,butwilltemporarilydisabletheflashmemoryandcrashthesystemifthememoryisusedforcode.

Bit2—Selectswhichsetofthetwolines/OExand/WExwillbedrivenformemoryaccessesinthisquadrant.

Bits1,0—Determineswhichofthethreechipselectlineswillbedrivenformemoryaccessestothisquadrant.

Allbitsofthecontrolregisterareinitializedtozeroonreset.

Table3.

MemoryBankControlRegisterx(MBxCR=14h+x)Bit(s)ValueDescription7:6004waitstates012waitstates101waitstates110waitstates51InvertaddressA1941InvertaddressA1831Write-protectmemorythisquadrant20Use/OE0,/WE01Use/OE1,/WE11:000Use/CS001Use/CS11xUse/CS2

Cwww.

rabbit.

com1TN202RabbitMemoryManagementInaNutshellTheRabbitCPUhasaMemoryManagementUnit(MMU)thatcontrolshowlogicalmemoryaddressesmapintophysicaladdresses,andaMemoryInterfaceUnitthatcontrolshowphysicaladdressesmapintoactualhardware.

TheDynamicCcompilerandlibrariesgenerallyhandlememorymappingdetailssothatmostDynamicCusersdon'thavetoconcernthemselveswithit,butsomeadvancedapplicationsmayneedtomanipulatetheMMUand/ortheMIU.

Forfurtherdetailsonmemorymanagement,seetheRabbitmicroprocessoruser'smanualforyourRabbitchip.

DefinitionsPhysical(orLinear)Addresses-20-bitaddressesrepresentingthe1Maddressspacethatlogicaladdressesmapinto.

Thehighest20-bitaddressis0xFFFFF.

ThedefaultaddressesintheDynamicCdevelopmentsystemflashstartatphysicaladdress0x00000andinRAMstartatphysicaladdress0x80000.

LogicalAddresses-16-bitaddressesrepresentinga64Kaddressspace.

Thehighest16-bitaddressis0x0FFFF.

MostRabbitinstructionsuselogicaladdresses.

ThelocationinphysicalmemorywheretheseaddressesmapintoiscompletelycontrollablebytheprogrammerviatheMMU.

Segment-Ablockoflogicalmemory;theblocksizesaremultiplesof4K(0x01000)Bank-A256KblockofPM,ona256Kboundary(0x40000).

TherearefourbanksavailablewithintheRabbitphysicaladdressspace.

Thestartingaddressofeachbankis0x00000,0x40000,0x80000,and0xC0000.

2www.

rabbit.

comTN202MemoryMappingUnitTheMMUtranslatesa16-bitlogicaladdresstoa20-bitphysicaladdress.

Thelogicaladdressspaceisdividedintofoursegments:xmem,stack,data,andbase.

ThexmemsegmentalwaysoccupiesE000h–FFFFh.

Theothersegmentsarelocatedfrom0000htoDFFFh,andareadjustableinsizetoanywherefrom0bytestoE000hbytes.

ThetotalsizeofallthreeisalwaysE000h.

ThestacksegmentstartsabovethedatasegmentandalwaysendsatDFFFh.

Thedatasegmentisalwaysabovethebasesegment.

Theboundariesbetweenthebasesegmentandthedatasegment,andbetweenthedataseg-mentandthestacksegmentaresetbyanMMUregister,SEGSIZE.

TheuppernibbleofSEGSIZErepre-sentsthestack-databoundary(in1000hbyteunits),andthelowernibblerepresentsthedata-baseboundary(in1000hbyteunits).

Eachoftheupperthreesegmentshasanassociatedsegmentregisterusedtomaplogicaladdressesthatfallwithinthesegmenttothephysicaladdressspace.

Fromtoptobottom,theyare:XPCSTACKSEGDATASEG.

Ineachcase,thephysicaladdressiscomputedbyshiftingthesegmentregisterleft12bits(multiplyingby1000h)andaddingittothel6-bitlogicaladdress.

Hereisthealgorithmforconvertinglogicaladdressestophysicaladdresses.

AbbreviationsLetSEGSIZE=XYhwhereXisthehighnibbleandYisthelownibble.

IfLA>=E000hPA=LA+(XPCx1000h)ElseIfLA>=X000hPA=LA+(STACKSEGx1000h)ElseIfLA>=Y000hPA=LA+(DATASEGx1000h)ElsePA=LAAnyofthesegmentregisterscanbeloadedwithanewvalidvalueatanytime,butthishastobedonewithgreatcare.

Forexample,ifcodeisexecutinginthexmemsegmentandtheXPCischanged,thenexecutionwillnotcontinueatthenextinstruction,butinsteadwillcontinueatthelocationinphysicalmemorywherethelogicaladdressofthenextinstructionmapsto.

ThisisbecausethePC(programcounter)registerholdsalogicaladdress.

LM-LogicalMemoryPM-PhysicalMemoryLA-LogicalAddress-addresswithintheLMPA-PhysicalAddress-addresswithinthePMTN202www.

rabbit.

com3ExampleTheMMUregistersaresetasfollows:XPC=0xF8SEGSIZE=0xD6STACKSEG=0x92DATASEG=0x7AThephysicaladdressofthebottomofthexmemsegmentisgivenby:0xF8000+0x0E000=0x06000(bit20,the21storcarrybit,isignored)Thephysicaladdressofthebottomofthestacksegmentisgivenby:0x92000+0x0D000=0x9F000Thephysicaladdressofthebottomofthedatasegmentisgivenby:0x7A000+0x06000=0x80000Notethatthedatasegmentstartsatthebeginningofthe"normal"RAMspaceand,fora128KRAM,thestacksegmentisallocated4K.

TherearespecialDynamicCfunctionstoaccessdataataspecificPA:root2xmem()andxmem2root().

Therearealsoseveralassemblylanguageinstructions:LDPformemoryaccessLCALLandLJPforbranchingNotethattheLDPinstructionsbypasstheMMUandgodirectlytotheMIU(seethenextsection).

Thefollowingdiagramillustratesthememorymappingdiscussedaboveusingthesamplecalculationswitha128Kflashanda128KRAM.

4www.

rabbit.

comTN202Figure1.

MemoryMappingBetweenLogicalAddressandPhysicalAddressMemoryInterfaceUnitTheMIUcontrolsmemoryaccessaftertheMMUdeterminesthephysicaladdress.

TherearefiveregistersassociatedwiththeMIU:MMIDRMB0CRMB1CRMB2CRMB3CRTheprimaryfunctionoftheMMIDRregisteristoallowthesystemtopermanentlyenable/CS1.

ThiscouldallowfasteraccesstotheRAMbykeepingthechipalwaysselected.

However,youwillneedtoinsurethatthe/OEand/or/WEsignalsarenotsharedwithanotherdevice.

EachofthefourMemoryBankControlRegistersMB0CR,MB1CR,MB2CRandMB3CR.

controlsone256Kquadrantofthe1Mphysicaladdressspace.

Theseregisterscontrolwaitstates,CS/WE/OElineusageandwriteprotection.

TheMBxCRregistersalsocanbesetuptoinvertaddresslinesA18andA19.

Ifbit4ofoneoftheseregis-tersisset,theMIUinvertsA18afterthelogicaltophysicalconversionisdonebytheMMU.

Ifbit5ofoneoftheseregistersisset,theMIUinvertsA19afterthelogicaltophysicalconversionisdonebytheMMU.

unusedunusedRAMFlashLogicalAddressSpaceXMEMStackDataBase0xFFFF0xE0000xD0000x60000x0000PhysicalAddressSpace0xFFFFF0xC00000xA00000x800000x400000x200000x000000x9F0000x06000TN202www.

rabbit.

com5Fora256Korsmallerdevice,addresslineinversionhasnoeffectsincethehighestaddresslineneededtoaddress256kisA17,butfora512Kdevice,thismeansthatwehaveaccesstothewhole512Kviaone256Kquadrantofphysicalmemory.

BecausewecancontrolA19aswell,each256Kquadrantofphysicaladdressescanactuallyaddressawhole1M.

This,incombinationwithdifferentCS/WE/OEcombinationscontrollablebythesameregisters,givestheRabbitaccessto6Mofmemorywithnoexternalgluelogic.

ExampleMB2CRissettomaptoCS1/WE1/OE1,andtheselinesgointoa512KRAM.

Thereforephysicaladdresses80000h-BFFFFh(quadrant2of0-3)maptooffsetsinthechipof00000h-3FFFFh(thelower256Kofthechip)usinglinesA0-A17withA18notasserted.

Nowwesetbit4ofMB2CRtoinvertA18.

Physicaladdresses80000h-BFFFFhnowmaptooffsetsinthechipof40000h-7FFFFh(theupper256Kofthechip.

)usinglinesA0-A17withA18asserted.

MMU/MIURegistersSegmentandMemoryBankRegistersTable1liststhedetailsaboutthesegmentregisters.

Table2liststhedetailsaboutthememorybankcontrolregisters.

Table1.

SegmentRegistersRegisterNameMnemonicI/OAddressR/WPostResetMMUInstruction/DataRegisterMMIDR10hR/Wxxx00000StackSegmentRegisterSTACKSEG11hR/W00000000LocatesstacksegmentinphysicalmemoryDataSegmentRegisterDATASEG12hR/W00000000LocatesdatasegmentinphysicalmemorySegmentSizeRegisterSEGSIZE13hR/W11111111Bits7.

.

4–boundaryaddressstacksegmentBits3.

.

0–boundaryaddressdatasegmentTable2.

MemoryBankControlRegistersRegisterNameMnemonicI/OAddressR/WPostResetMemoryBank0ControlRegisterMB0CR14hW00000000MemoryBank1ControlRegisterMB1CR15hWxxxxxxxxMemoryBank2ControlRegisterMB2CR16hWxxxxxxxxMemoryBank3ControlRegisterMB3CR17hWxxxxxxxx6www.

rabbit.

comTN202MemoryBankControlRegisterFunctionsThistabledetailsthefunctionalityofthememorybankcontrolregistersandthenecessarybitvalues.

Table3describestheoperationofthefourmemorybankcontrolregisters.

Theregistersarewrite-only.

Eachregistercontrolsonequadrantinthe1Maddressspace.

Bits7,6—Thenumberofwaitstatesusedinaccesstothisquadrant.

Withoutwaitstates,readrequires2clocksandwriterequires3clocks.

Thewaitstateaddstothesenumbers.

Bits5,4—Thesebitsallowtheupperaddresslinestobeinverted.

Thisinversionoccursafterthelogicthatselectsthebankregister,sosettingtheselineshasnoeffectonwhichbankregisterisused.

Theinversionmaybeusedtoinstalla1Mmemorychipinthespacenormallyallocatedtoa256Kchip.

Thelargermemorycanthenbeaccessedas4pagesof256Keach.

Thereisnoeffectoutsidethequadrantthatthememorybankcontrolregisteriscontrolling.

Bit3—Inhibitsthewritepulsetomemoryaccessedinthisquadrant.

Usefulforprotectingflashmemoryfromaninadvertentwritepulse,whichwillnotactuallywritetotheflashbecauseitispro-tectedbylockcodes,butwilltemporarilydisabletheflashmemoryandcrashthesystemifthememoryisusedforcode.

Bit2—Selectswhichsetofthetwolines/OExand/WExwillbedrivenformemoryaccessesinthisquadrant.

Bits1,0—Determineswhichofthethreechipselectlineswillbedrivenformemoryaccessestothisquadrant.

Allbitsofthecontrolregisterareinitializedtozeroonreset.

Table3.

MemoryBankControlRegisterx(MBxCR=14h+x)Bit(s)ValueDescription7:6004waitstates012waitstates101waitstates110waitstates51InvertaddressA1941InvertaddressA1831Write-protectmemorythisquadrant20Use/OE0,/WE01Use/OE1,/WE11:000Use/CS001Use/CS11xUse/CS2

- unitsphysicalmemory相关文档

- eventphysicalmemory

- bringphysicalmemory

- maintainsphysicalmemory

- reasonsphysicalmemory

- enabledphysicalmemory

- specificphysicalmemory

美得云(15元/月)美国cera 2核4G 15元/月 香港1核 1G 3M独享

美得云怎么样?美得云好不好?美得云是第一次来推广软文,老板人脾气特别好,能感觉出来会用心对待用户。美得云这次为大家提供了几款性价比十分高的产品,美国cera 2核4G 15元/月 香港1核 1G 3M独享 15元/月,并且还提供了免费空间给大家使用。嘻嘻 我也打算去白嫖一个空间了。新用户注册福利-8折优惠码:H2dmBKbF 截止2021.10.1结束。KVM架构,99.99%高可用性,依托BGP...

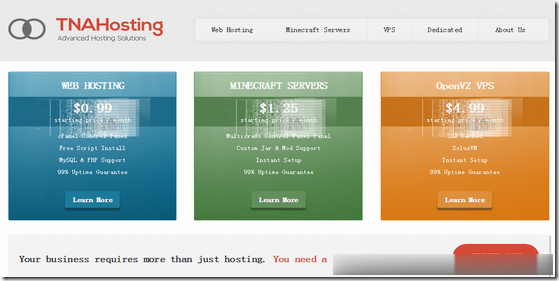

TNAHosting($5/月)4核/12GB/500GB/15TB/芝加哥机房

TNAHosting是一家成立于2012年的国外主机商,提供VPS主机及独立服务器租用等业务,其中VPS主机基于OpenVZ和KVM架构,数据中心在美国芝加哥机房。目前,商家在LET推出芝加哥机房大硬盘高配VPS套餐,再次刷新了价格底线,基于OpenVZ架构,12GB内存,500GB大硬盘,支持月付仅5美元起。下面列出这款VPS主机配置信息。CPU:4 cores内存:12GB硬盘:500GB月流...

ZJI:香港物理服务器,2*E5-2630L/32G/480G SSD/30Mbps/2IP/香港BGP,月付520元

zji怎么样?zji是一家老牌国人主机商家,公司开办在香港,这个平台主要销售独立服务器业务,和hostkvm是同一样,两个平台销售的产品类别不一平,商家的技术非常不错,机器非常稳定。昨天收到商家的优惠推送,目前针对香港邦联四型推出了65折优惠BGP线路服务器,性价比非常不错,有需要香港独立服务器的朋友可以入手,非常适合做站。zji优惠码:月付/年付优惠码:zji 物理服务器/VDS/虚拟主机空间订...

physicalmemory为你推荐

-

atmosphereios11namesgraph支持ipad支持ipadwin7如何关闭445端口如何关闭WIN7自动配置 IPV4 地址 169.254联通iphone4联通iphone4跟苹果的iphone4有什么不一样? 比如少了什么功能? 还是什么的?css选择器请给出三种Css选择器并举例说明迅雷下载速度迅雷限制下载速度要设置多少迅雷下载速度迅雷下载速度与什么有关?google统计怎样将Google分析转换成中文显示Google中文专题交流