bringphysicalmemory

physicalmemory 时间:2021-05-19 阅读:()

Lecture20:CacheHierarchies,VirtualMemoryToday'stopics:CachehierarchiesVirtualmemoryReminder:Assignment8willbepostedsoon(dueTue11/21)ExampleAccessPattern8-bytewords101000Direct-mappedcache:eachaddressmapstoauniqueaddressByteaddressTagCompareDataarrayTagarrayAssumethataddressesare8bitslongHowmanyofthefollowingaddressrequestsarehits/misses4,7,10,13,16,68,73,78,83,88,4,7,10…IncreasingLineSize32-bytecachelinesizeorblocksize10100000ByteaddressTagDataarrayTagarrayOffsetAlargecachelinesizesmallertagarray,fewermissesbecauseofspatiallocalityAssociativity10100000ByteaddressTagDataarrayTagarraySetassociativityfewerconflicts;wastedpowerbecausemultipledataandtagsarereadWay-1Way-2CompareAssociativity10100000ByteaddressTagDataarrayTagarrayHowmanyoffset/index/tagbitsifthecachehas64sets,eachsethas64bytes,4waysWay-1Way-2CompareExample32KB4-wayset-associativedatacachearraywith32bytelinesizesHowmanysetsHowmanyindexbits,offsetbits,tagbitsHowlargeisthetagarrayCacheMissesOnawritemiss,youmayeitherchoosetobringtheblockintothecache(write-allocate)ornot(write-no-allocate)Onareadmiss,youalwaysbringtheblockin(spatialandtemporallocality)–butwhichblockdoyoureplacenochoiceforadirect-mappedcacherandomlypickoneofthewaystoreplacereplacethewaythatwasleast-recentlyused(LRU)FIFOreplacement(round-robin)WritesWhenyouwriteintoablock,doyoualsoupdatethecopyinL2write-through:everywritetoL1writetoL2write-back:marktheblockasdirty,whentheblockgetsreplacedfromL1,writeittoL2WritebackcoalescesmultiplewritestoanL1blockintooneL2writeWritethroughsimplifiescoherencyprotocolsinamultiprocessorsystemastheL2alwayshasacurrentcopyofdataTypesofCacheMissesCompulsorymisses:happensthefirsttimeamemorywordisaccessed–themissesforaninfinitecacheCapacitymisses:happensbecausetheprogramtouchedmanyotherwordsbeforere-touchingthesameword–themissesforafully-associativecacheConflictmisses:happensbecausetwowordsmaptothesamelocationinthecache–themissesgeneratedwhilemovingfromafully-associativetoadirect-mappedcacheVirtualMemoryProcessesdealwithvirtualmemory–theyhavetheillusionthataverylargeaddressspaceisavailabletothemThereisonlyalimitedamountofphysicalmemorythatissharedbyallprocesses–aprocessplacespartofitsvirtualmemoryinthisphysicalmemoryandtherestisstoredondisk(calledswapspace)Thankstolocality,diskaccessislikelytobeuncommonThehardwareensuresthatoneprocesscannotaccessthememoryofadifferentprocessAddressTranslationThevirtualandphysicalmemoryarebrokenupintopagesVirtualaddress8KBpagesizepageoffsetvirtualpagenumberTranslatedtophysicalpagenumberPhysicaladdress13MemoryHierarchyPropertiesAvirtualmemorypagecanbeplacedanywhereinphysicalmemory(fully-associative)ReplacementisusuallyLRU(sincethemisspenaltyishuge,wecaninvestsomeefforttominimizemisses)Apagetable(indexedbyvirtualpagenumber)isusedfortranslatingvirtualtophysicalpagenumberThepagetableisitselfinmemoryTLBSincethenumberofpagesisveryhigh,thepagetablecapacityistoolargetofitonchipAtranslationlookasidebuffer(TLB)cachesthevirtualtophysicalpagenumbertranslationforrecentaccessesATLBmissrequiresustoaccessthepagetable,whichmaynotevenbefoundinthecache–twoexpensivememorylook-upstoaccessonewordofdata!

AlargepagesizecanincreasethecoverageoftheTLBandreducethecapacityofthepagetable,butalsoincreasesmemorywastageTLBandCacheIsthecacheindexedwithvirtualorphysicaladdressToindexwithaphysicaladdress,wewillhavetofirstlookuptheTLB,thenthecachelongeraccesstimeMultiplevirtualaddressescanmaptothesamephysicaladdress–mustensurethatthesedifferentvirtualaddresseswillmaptothesamelocationincache–else,therewillbetwodifferentcopiesofthesamephysicalmemorywordDoesthetagarraystorevirtualorphysicaladdressesSincemultiplevirtualaddressescanmaptothesamephysicaladdress,avirtualtagcomparisoncanflagamissevenifthecorrectphysicalmemorywordispresentCacheandTLBPipelineTLBVirtualaddressTagarrayDataarrayPhysicaltagcomparionVirtualpagenumberVirtualindexOffsetPhysicalpagenumberPhysicaltagVirtuallyIndexed;PhysicallyTaggedCacheBadEventsConsiderthelongestlatencypossibleforaloadinstruction:TLBmiss:mustlookuppagetabletofindtranslationforv.

pagePCalculatethevirtualmemoryaddressforthepagetableentrythathasthetranslationforpageP–let'ssay,thisisv.

pageQTLBmissforv.

pageQ:willrequirenavigationofahierarchicalpagetable(let'signorethiscasefornowandassumewehavesucceededinfindingthephysicalmemorylocation(R)forpageQ)AccessmemorylocationR(findthiseitherinL1,L2,ormemory)Wenowhavethetranslationforv.

pageP–putthisintotheTLBWenowhaveaTLBhitandknowthephysicalpagenumber–thisallowsustodotagcomparisonandchecktheL1cacheforahitIfthere'samissinL1,checkL2–ifthatmisses,checkinmemoryAtanypoint,ifthepagetableentryclaimsthatthepageisondisk,flagapagefault–theOSthencopiesthepagefromdisktomemoryandthehardwareresumeswhatitwasdoingbeforethepagefault…phew!

TitleBullet

AlargepagesizecanincreasethecoverageoftheTLBandreducethecapacityofthepagetable,butalsoincreasesmemorywastageTLBandCacheIsthecacheindexedwithvirtualorphysicaladdressToindexwithaphysicaladdress,wewillhavetofirstlookuptheTLB,thenthecachelongeraccesstimeMultiplevirtualaddressescanmaptothesamephysicaladdress–mustensurethatthesedifferentvirtualaddresseswillmaptothesamelocationincache–else,therewillbetwodifferentcopiesofthesamephysicalmemorywordDoesthetagarraystorevirtualorphysicaladdressesSincemultiplevirtualaddressescanmaptothesamephysicaladdress,avirtualtagcomparisoncanflagamissevenifthecorrectphysicalmemorywordispresentCacheandTLBPipelineTLBVirtualaddressTagarrayDataarrayPhysicaltagcomparionVirtualpagenumberVirtualindexOffsetPhysicalpagenumberPhysicaltagVirtuallyIndexed;PhysicallyTaggedCacheBadEventsConsiderthelongestlatencypossibleforaloadinstruction:TLBmiss:mustlookuppagetabletofindtranslationforv.

pagePCalculatethevirtualmemoryaddressforthepagetableentrythathasthetranslationforpageP–let'ssay,thisisv.

pageQTLBmissforv.

pageQ:willrequirenavigationofahierarchicalpagetable(let'signorethiscasefornowandassumewehavesucceededinfindingthephysicalmemorylocation(R)forpageQ)AccessmemorylocationR(findthiseitherinL1,L2,ormemory)Wenowhavethetranslationforv.

pageP–putthisintotheTLBWenowhaveaTLBhitandknowthephysicalpagenumber–thisallowsustodotagcomparisonandchecktheL1cacheforahitIfthere'samissinL1,checkL2–ifthatmisses,checkinmemoryAtanypoint,ifthepagetableentryclaimsthatthepageisondisk,flagapagefault–theOSthencopiesthepagefromdisktomemoryandthehardwareresumeswhatitwasdoingbeforethepagefault…phew!

TitleBullet

- bringphysicalmemory相关文档

- eventphysicalmemory

- maintainsphysicalmemory

- reasonsphysicalmemory

- enabledphysicalmemory

- specificphysicalmemory

- unitsphysicalmemory

ReliableSite怎么样,月付$95美国洛杉矶独立服务器

ReliableSite怎么样?ReliableSite好不好。ReliableSite是一家成立于2006年的老牌美国商家,主要经营美国独立服务器租赁,数据中心位于:洛杉矶、迈阿密、纽约,带宽1Gbps起步,花19美元/月即可升级到10Gbps带宽,月流量150T足够各种业务场景使用,且免费提供20Gbps DDoS防护。当前商家有几款大硬盘美国独服,地点位于美国洛杉矶或纽约机房,机器配置很具有...

ThomasHost(月付5美元)美国/法国/英国/加拿大KVM,支持Windows

ThomasHost域名注册自2012年,部落最早分享始于2016年,还算成立了有几年了,商家提供基于KVM架构的VPS,数据中心包括美国、法国、英国、加拿大和爱尔兰等6个地区机房,VPS主机套餐最低2GB内存起步,支持Windows或者Linux操作系统,1Gbps端口不限制流量。最近商家提供了一个5折优惠码,优惠后最低套餐月付5美元起。下面列出部分套餐配置信息。CPU:1core内存:2GB硬...

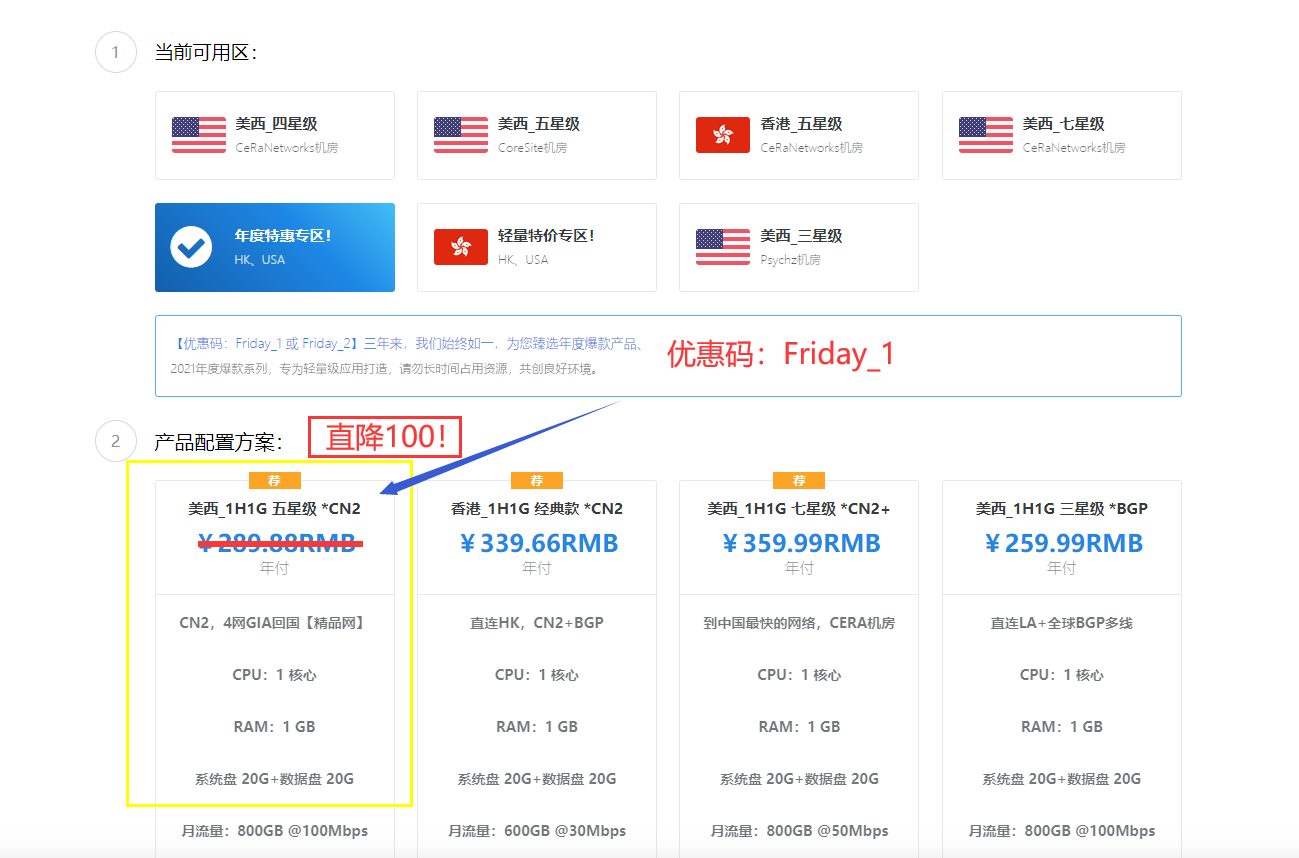

极光KVM(限时16元),洛杉矶三网CN2,cera机房,香港cn2

极光KVM创立于2018年,主要经营美国洛杉矶CN2机房、CeRaNetworks机房、中国香港CeraNetworks机房、香港CMI机房等产品。其中,洛杉矶提供CN2 GIA、CN2 GT以及常规BGP直连线路接入。从名字也可以看到,VPS产品全部是基于KVM架构的。极光KVM也有明确的更换IP政策,下单时选择“IP保险计划”多支付10块钱,可以在服务周期内免费更换一次IP,当然也可以不选择,...

physicalmemory为你推荐

-

伺服器chrome支持ipad支持ipad支持ipadcss3圆角用CSS3怎么实现圆角边框?win7telnetwindows7旗舰版中telnet在哪x-routerX-TRAlL是什么意思iphonewifi苹果wifi版和4G版是什么意思,有什么区别吗google图片搜索谁能教我怎么在手机用google的图片搜索啊!!!谷歌sbgoogle一下"SB",虽然显示的是baidu排第一,链接的不是baidu.