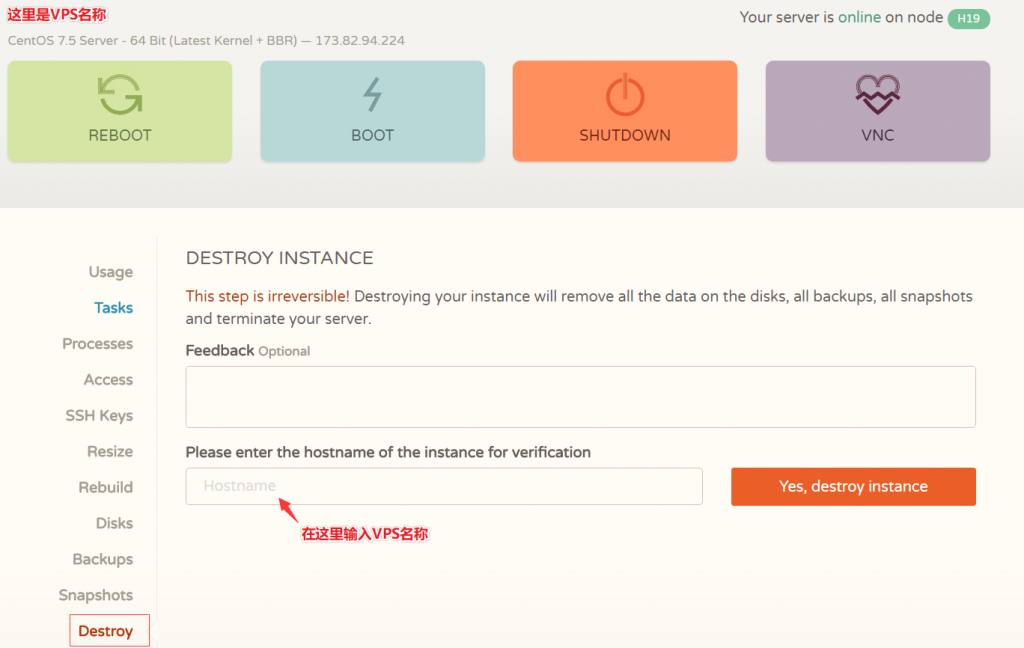

cyclehaole10.com

haole10.com 时间:2021-03-19 阅读:()

DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014DS92LX1621/DS92LX162210-50MHzDC-BalancedChannelLinkIIISerializerandDeserializerwithBi-DirectionalControlChannelCheckforSamples:DS92LX1621,DS92LX16221FEATURESSERPackage:32PinWQFN(5mmx5mm)DESPackage:40PinWQFN(6mmx6mm)2ConfigurableDataThroughput–12–bit(min)upto600Mbits/secAPPLICATIONS–16–bit(def)upto800Mbits/secIndustrialDisplays,TouchScreens–18–bit(max)upto900Mbits/secMedicalImaging10MHzto50MHzInputClockSupportEmbeddedClockwithDCBalancedCodingtoDESCRIPTIONSupportAC-CoupledInterconnectsTheDS92LX1621/DS92LX1622chipsetoffersaCapabletoDriveupto10MetersShieldedChannelLinkIIIinterfacewithahigh-speedforwardTwisted-Pairchannelandafull-duplexbackchannelfordatatransmissionoverasingledifferentialpair.

TheBi-DirectionalControlInterfaceChannelwithSerializer/DeserializerpairistargetedfordirectI2CSupportconnectionsbetweenautomotivecamerasystemsI2CInterfaceforDeviceConfiguration.

Single-andHostController/ElectronicControlUnit(ECU).

pinIDAddressingTheprimarytransportsends16bitsofimagedata16–bitDataPayloadwithCRC(Cyclicoverasinglehigh-speedserialstreamtogetherwithalowlatencybi-directionalcontrolchanneltransportRedundancyCheck)forCheckingDatathatsupportsI2C.

Includedwiththe16-bitpayloadisIntegritywithProgrammableDataaselectabledataintegrityoptionforCRC(CyclicTransmissionErrorDetectionandInterruptRedundancyCheck)orparitybittomonitorControltransmissionlinkerrors.

UsingTI'sembeddedclockUpto6ProgrammableGPIO'stechnologyallowstransparentfull-duplexAT-SPEEDBISTDiagnosisFeaturetoValidatecommunicationoverasingledifferentialpair,carryingasymmetricalbi-directionalcontrolinformationwithoutLinkIntegritythedependencyofvideoblankingintervals.

ThisIndividualPower-DownControlsforBothSERsingleserialstreamsimplifiestransferringawidedataandDESbusoverPCBtracesandcablebyeliminatingtheUser-SelectableClockEdgeforParallelDataskewproblemsbetweenparalleldataandclockonBothSERandDESpaths.

ThissignificantlysavessystemcostbynarrowingdatapathsthatinturnreducePCBlayers,IntegratedTerminationResistorscablewidth,andconnectorsizeandpins.

1.

8V-or3.

3V-CompatibleParallelBusInterfaceInaddition,theDeserializerinputsprovideSinglePowerSupplyat1.

8VequalizationcontroltocompensateforlossfromtheIEC61000–4–2ESDCompliantmediaoverlongerdistances.

InternalDCbalancedNoReferenceClockRequiredonDeserializerencoding/decodingisusedtosupportAC-Coupledinterconnects.

ProgrammableReceiveEqualizationLOCKOutputReportingPintoEnsureLinkThesleepfunctionprovidesapower-savingsmodeStatusandaremotewakeupinterruptforsignalingofaremotedevice.

EMI/EMCMitigationTheSerializerisofferedina32-pinWQFNpackage,–DESProgrammableSpreadSpectrumandDeserializerisofferedina40-pinWQFN(SSCG)Outputspackage.

–DESReceiverStaggeredOutputsTemperatureRange40°Cto+85°C1Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

2Alltrademarksarethepropertyoftheirrespectiveowners.

PRODUCTIONDATAinformationiscurrentasofpublicationdate.

Copyright2010–2014,TexasInstrumentsIncorporatedProductsconformtospecificationsperthetermsoftheTexasInstrumentsstandardwarranty.

Productionprocessingdoesnotnecessarilyincludetestingofallparameters.

DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTypicalApplicationDiagramFigure1.

TypicalApplicationCircuitBlockDiagramsFigure2.

BlockDiagramFigure3.

ApplicationBlockDiagram2SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014DS92LX1621PinDiagramTopViewFigure4.

Serializer-DS92LX162132-PinWQFN(RTVPackage)DS92LX1621SerializerPINDESCRIPTIONSPinNamePinNo.

I/O,TypeDescriptionLVCMOSPARALLELINTERFACE32,31,30,29,27,26,24,23,Inputs,LVCMOSw/DIN[13:0]Paralleldatainputs.

22,21,20,19,pulldown18,17Inputs,LVCMOSw/HSYNC1Paralleldatainput14,typicallyusedasHorizontalSYNCInputpulldownInputs,LVCMOSw/VSYNC2Paralleldatainput15,typicallyusedasVerticalSYNCInputpulldownInput,LVCMOSw/PCLK3PixelClockInputPin.

StrobeedgesetbyTRFBcontrolregister.

pulldownGENERALPURPOSEINPUTOUTPUT(GPIO)DIN[3:0]/DIN[3:0]general-purposepinscanbeindividuallyconfiguredaseitherinputs20,19,18,17Input/Output,DigitalGPIO[5:2]oroutputs;usedtocontrolandrespondtovariouscommands.

General-purposepinscanbeindividuallyconfiguredaseitherinputsorGPIO[1:0]16,15Input/Output,Digitaloutputs;usedtocontrolandrespondtovariouscommands.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback3ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comDS92LX1621SerializerPINDESCRIPTIONS(continued)PinNamePinNo.

I/O,TypeDescriptionSERIALCONTROLBUS-I2CCOMPATIBLEClocklinefortheserialcontrolbuscommunicationSCL4Input/Output,DigitalSCLrequiresanexternalpull-upresistortoVDDIO.

Input/Output,OpenDatalinefortheserialcontrolbuscommunicationSDA5DrainSDArequiresanexternalpull-upresistortoVDDIO.

I2CModeSelectInput,LVCMOSw/M/S8M/S=L,Master(default);devicegeneratesanddrivestheSCLclocklinepulldownM/S=H,Slave;deviceacceptsSCLclockinputContinuousAddressDecoderInputpintoselecttheSlaveDeviceAddress.

CAD6Input,analogInputisconnecttoexternalresistordividertoprogrammableDeviceIDaddress(SeeFigure29).

CONTROLANDCONFIGURATIONPowerdownModeInputPin.

Input,LVCMOSw/PDB=H,TransmitterisenabledandisON.

PDB9pulldownPDB=L,TransmitterisinSleep(PowerDown).

WhenthetransmitterisintheSLEEPstate,thePLLisshutdown,andIDDisminimized.

Input,LVCMOSw/RES7Reserved.

ThispinMUSTbetiedLOW.

pulldownChannelLinkIIIINTERFACEDOUT+13Input/Output,CMLNon-invertingdifferentialoutput,back-channelinput.

DOUT-12Input/Output,CMLInvertingdifferentialoutput,back-channelinput.

PowerandGroundVDDPLL10Power,AnalogPLLPower,1.

8V±5%VDDT11Power,AnalogTxAnalogPower,1.

8V±5%VDDCML14Power,AnalogLVDS&BCDrPower,1.

8V±5%VDDD28Power,DigitalDigitalPower,1.

8V±5%VDDIO25Power,DigitalPowerforinputstage,Thesingle-endedinputsarepoweredfromVDDIO.

VSSDAPGround,DAPDAPmustbegrounded.

Connecttogroundplanewithatleast9vias.

4SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014DS92LX1622PINDIAGRAMTopViewFigure5.

Deserializer-DS92LX162240-PinWQFN(RTAPackage)DS92LX1622DeserializerPINDESCRIPTIONSPinNamePinNo.

I/O,TypeDescriptionLVCMOSPARALLELINTERFACE9,10,11,12,14,15,17,18,ROUT[13:0]Outputs,LVCMOSParalleldataoutputs.

19,20,21,22,23,24HSYNC7Output,LVCMOSParalleldataoutput14,typicallyusedasHorizontalSYNCoutputVSYNC6Output,LVCMOSParalleldataoutput14,typicallyusedasVerticalSYNCoutputPixelClockOutputPin.

PCLK5Output,LVCMOSStrobeedgesetbyRRFBcontrolregisterGeneralPurposeInputOutput(GPIO)ROUT[3:0]/ROUT[3:0]general-purposepinscanbeindividuallyconfiguredaseitherinputs21,22,23,24Input/Output,DigitalGPIO[5:2]oroutputs;usedtocontrolandrespondtovariouscommands.

General-purposepinscanbeindividuallyconfiguredaseitherinputsoroutputs;GPIO[1:0]26,27Input/Output,Digitalusedtocontrolandrespondtovariouscommands.

SERIALCONTROLBUS-I2CCOMPATIBLEClocklinefortheserialcontrolbuscommunicationSCL3Input/Output,DigitalSCLrequiresanexternalpull-upresistortoVDDIO.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback5ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comDS92LX1622DeserializerPINDESCRIPTIONS(continued)PinNamePinNo.

I/O,TypeDescriptionInput/Output,OpenDatalineforserialcontrolbuscommunicationSDA2DrainSDArequiresanexternalpull-upresistortoVDDIO.

I2CModeSelectInput,LVCMOSw/M/S40M/S=L,Master;devicegeneratesanddrivestheSCLclocklinepullupM/S=H,Slave(default);deviceacceptsSCLclockinputContinuousAddressDecoderInputpintoselecttheSlaveDeviceAddress.

CAD1Input,analogInputisconnecttoexternalresistordividertoprogrammableDeviceIDaddress(SeeFigure29)CONTROLANDCONFIGURATIONPowerdownModeInputPin.

PDB=H,ReceiverisenabledandisON.

Input,LVCMOSw/PDB29PDB=L,ReceiverisinSleep(Powerdownmode).

WhentheReceiverisinthepulldownSLEEPstate,theLVCMOSOutputsareinTRI-STATE,thePLLisshutdownandIDDisminimized.

LOCKStatusOutputPin.

LOCK=H,PLLisLocked,outputsareactiveLOCK28Output,LVCMOSLOCK=L,PLLisunlocked,ROUTandPCLKoutputstatesarecontrolledbyOSS_SEL.

MaybeusedasLinkStatus.

WhenBISTEN=L;NormaloperationPASS31Output,LVCMOSPASSishightoindicatenoerrorsaredetected.

ThePASSpinassertslowtoindicateaCRCerrorwasdetectedonthelink.

Reserved.

RES32,33,39-Pin39:ThispinMUSTbetiedLOW.

Pins32,33:Leavepinopen.

BISTMODEBISTEnablePin.

Input,LVCMOSw/BISTEN37BISTEN=H,BISTModeisenabled.

pulldownBISTEN=L,BISTModeisdisabled.

PASSOutputPinforBISTmode.

PASS=H,ERRORFREETransmissionPASS31Output,LVCMOSPASS=L,oneormoreerrorsweredetectedinthereceivedpayload.

LeaveOpenifunused.

Routetotestpoint(pad)recommended.

ChannelLinkIIIINTERFACERIN+35Input/Output,CMLNoninvertingdifferentialinput,backchanneloutput.

RIN-36Input/Output,CMLInvertingdifferentialinput,backchanneloutput.

POWERANDGROUNDSSCGPower,1.

8V±5%VDDSSCG4DigitalPowerPowersupplymustbeconnectregardlessifSSCGfunctionisinoperationTTLOutputBufferPower,Thesingle-endedoutputsandcontrolinputareVDDOR1/2/325,16,8DigitalPowerpoweredfromVDDIO.

VDDIOcanbeconnectedtoa1.

8V±5%or3.

3V±10%VDDD13DigitalPowerDigitalCorePower,1.

8V±5%VDDR30AnalogPowerRxAnalogPower,1.

8V±5%VDDCML34AnalogPowerBi-DirectionalControlChannelDriverPower,1.

8V±5%VDDPLL38AnalogPowerPLLPower,1.

8V±5%VSSDAPGroundDAPmustbegrounded.

Connecttothegroundplanewithatleast16vias.

Thesedeviceshavelimitedbuilt-inESDprotection.

TheleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoamduringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates.

6SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014AbsoluteMaximumRatings(1)(2)SupplyVoltage(VDD1V8)0.

3Vto+2.

5VSupplyVoltage(VDD3V3)0.

3Vto+4.

0VLVCMOSInputVoltage(VDD1V8)0.

3Vto+(VDD1V8+0.

3V)LVCMOSInputVoltage(VDD3V3)0.

3Vto+(VDD3V3+0.

3V)LVCMOSOutputVoltage(VDD)0.

3Vto+(VDD+0.

3V)CMLDriverI/OVoltage(VDD1V8)0.

3Vto(VDD1V8+0.

3V)CMLReceiverI/OVoltage(VDD1V8)0.

3Vto(VDD1V8+0.

3V)JunctionTemperature+150°CStorageTemperature65°Cto+150°CMaximumPackagePowerDissipationCapacity1/θJA°C/Wabove+25°PackageDerating:DS92LX162132LWQFNθJA(basedon9thermalvias)34.

3°C/WθJC(basedon9thermalvias)6.

9°C/WMaximumPackagePowerDissipationCapacityPackage1/θJA°C/Wabove+25°PackageDerating:DS92LX162240LWQFNθJA(basedon16thermalvias)28.

0°C/WθJC(basedon16thermalvias)4.

4°C/WESDRating(IEC61000–4–2)RD=330,CS=150pFAirDischarge≥±25kV(DOUT+,DOUT-,RIN+,RIN-)ContactDischarge≥±10kV(DOUT+,DOUT-,RIN+,RIN-)ESDRating(HBM)≥±8kV(1)"AbsoluteMaximumRatings"indicatelimitsbeyondwhichdamagetothedevicemayoccur,includinginoperabilityanddegradationofdevicereliabilityand/orperformance.

Functionaloperationofthedeviceand/ornon-degradationattheAbsoluteMaximumRatingsorotherconditionsbeyondthoseindicatedintheRecommendedOperatingConditionsisnotimplied.

TheRecommendedOperatingConditionsindicateconditionsatwhichthedeviceisfunctional;thedeviceshouldnotbeoperatedbeyondsuchconditions.

(2)IfMilitary/Aerospacespecifieddevicesarerequired,pleasecontacttheTexasInstrumentsSalesOffice/Distributorsforavailabilityandspecifications.

RecommendedOperatingConditionsMinNomMaxUnitsVDD(1.

8V)1.

711.

81.

89VVDDIO(1.

8VMode)1.

711.

81.

89VVDDIO(3.

3VMode)33.

33.

6VSupplyNoiseVDDn(1.

8V)25mVp-pVDDIO(1.

8V)25mVp-pVDD3V350mVp-pOperatingFreeAirTemperature(TA)-40+25+85°CInputClockRate1050MHzCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback7ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comSerializerElectricalCharacteristics(1)(2)(3)Overrecommendedoperatingsupplyandtemperaturerangesunlessotherwisespecified.

SymbolParameterConditionsMinTypMaxUnitsLVCMOSDCSPECIFICATIONS3.

3VI/O(SERINPUTS,DESOUTPUTS,GPIO,CONTROLINPUTSANDOUTPUTS)VIHHighLevelInputVoltageVIN=3.

0Vto3.

6V2.

0VINVVILLowLevelInputVoltageVIN=3.

0Vto3.

6VGND0.

8VVIN=0Vor3.

6VIINInputCurrent-20±1+20AVIN=3.

0Vto3.

6VVOHHighLevelOutputVoltageVDDIO=3.

0Vto3.

6V2.

4VDDIOVVDDIO=3.

0Vto3.

6VVOLLowLevelOutputVoltageGND0.

4VIOH=+4mASerializerGPIO-24OutputsOutputShortCircuitIOSVOUT=0VmACurrentDeserializer-39LVCMOSOutputsTRI-STATEOutputPDB=0V,IOZLVCMOSOutputs-20±1+20ACurrentVOUT=0VorVDDLVCMOSDCSPECIFICATIONS1.

8VI/O(TXINPUTS,RXOUTPUTS,GPIO,CONTROLINPUTSANDOUTPUTS)VIHHighLevelInputVoltageVIN=1.

71Vto1.

89V0.

65VINVIN+0.

3VVILLowLevelInputVoltageVIN=1.

71Vto1.

89VGND0.

35VINVIN=0Vor1.

89VIINInputCurrent-20±1+20AVIN=1.

71Vto1.

89VVDDIO=1.

71Vto1.

89VVOHHighLevelOutputVoltageVDDIO-0.

45VDDIOVIOH=4mAVDDIO=1.

71Vto1.

89VVOLLowLevelOutputVoltageGND0.

45VIOL=+4mASerializerGPIO-11OutputsOutputShortCircuitIOSVOUT=0V(4)mACurrentDeserializer-20LVCMOSOutputsTRI-STATEOutputPDB=0V,LVCMOSOutputsIOZ-20±1+20ACurrentVOUT=0VorVDDCMLDRIVERDCSPECIFICATIONS(DOUT+,DOUT-)|VOD|OutputDifferentialVoltageRT=100268340412mVOutputDifferentialVoltageΔVODRL=100150mVUnbalanceOutputDifferentialOffsetVDD(MIN)-VDD(MAX)-VOSRL=100(SeeFigure10)VDD-VODVVoltageVOD(MAX)VOD(MIN)ΔVOSOffsetVoltageUnbalanceRL=100150mVOutputShortCircuitDOUT+/-=0V,IOS-27mACurrentPDB=LorH(4)DifferentialInternalRTDifferentialacrossDOUT+andDOUT-80100120TerminationResistanceCMLRECEIVERDCSPECIFICATIONS(RIN+,RIN-)DifferentialThresholdVTH+90HighVoltageSeeFigure12mVDifferentialThresholdLowVTL-90Voltage(1)TheElectricalCharacteristicstableslistguaranteedspecificationsunderthelistedRecommendedOperatingConditionsexceptasotherwisemodifiedorspecifiedbytheElectricalCharacteristicsConditionsand/orNotes.

Typicalspecificationsareestimationsonlyandarenotguaranteed.

(2)Currentintodevicepinsisdefinedaspositive.

Currentoutofadevicepinisdefinedasnegative.

VoltagesarereferencedtogroundexceptVOD,ΔVOD,VTHandVTLwhicharedifferentialvoltages.

(3)Typicalvaluesrepresentmostlikelyparametricnormsat1.

8Vor3.

3V,TA=+25°C,andattheRecommendedOperationConditionsatthetimeofproductcharacterizationandarenotguaranteed.

(4)Specificationisguaranteedbycharacterizationandisnottestedinproduction.

8SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014SerializerElectricalCharacteristics(1)(2)(3)(continued)Overrecommendedoperatingsupplyandtemperaturerangesunlessotherwisespecified.

SymbolParameterConditionsMinTypMaxUnitsDifferentialInputVoltageVINRIN+-RIN-180mVRangeVIN=VDDor0V,IINInputCurrent-20±1+20AVDD=1.

89VDifferentialInternalRTDifferentialacrossRIN+andRIN-80100120TerminationResistanceSER/DESSUPPLYCURRENT*DIGITAL,PLL,ANDANALOGVDDSRT=100Serializer(Tx)WORSTCASEpattern6290VDDn=1.

89V,TotalSupplyCurrent(SeeFigure7)IDDTf=50MHzmAMode(includesloadDefaultRegistersRT=100current)55RANDOMPRBS-7patternVDDn=1.

89V,f=50MHz25Serializer(Tx)RT=100DefaultRegistersIDDIOTVDDIOSupplyCurrentWORSTCASEpatternmAVDDn=3.

6V,(includesloadcurrent)(SeeFigure7)f=50MHz715DefaultRegistersVDD=1.

89V370775IDDTZSerializer(Tx)SupplyPDB=0V;AllotherVDDIO=1.

89V55125ACurrentPower-downLVCMOSInputs=0VIDDIOTZVDDIO=3.

6V65135VDDn=1.

89Vf=50MHzCL=8pFSSCG[3:0]=ON6096WORSTCASEPatternDeserializer(Rx)SupplyDefaultRegisters(SeeFigure7)IDDRCurrent(includesloadcurrent)VDDn=3.

6Vf=50MHzCL=8pFDefaultRegisters53WORSTCASEPatternmAVDDIO=1.

89Vf=50MHzCL=8pFDefaultRegisters1625WORSTCASEPatternDeserializer(Rx)VDDIO(SeeFigure7)IDDIORSupplyCurrent(includesloadcurrent)VDDIO=3.

6Vf=50MHzCL=8pFDefaultRegisters3864WorstCasePatternVDDn=1.

89V42400IDDRZDeserializer(Rx)SupplyPDB=0V;AllotherVDDIO=1.

89V840ACurrentPower-downLVCMOSInputs=0VIDDIORZVDDIO=3.

6V350800Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback9ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comRecommendedSerializerTimingforPCLK(1)(2)Overrecommendedoperatingsupplyandtemperaturerangesunlessotherwisespecified.

SymbolParameterConditionsMinTypMaxUnitstTCPTransmitClockPeriod20T100nsTransmitClockInputHightTCIH0.

4T0.

5T0.

6TnsTime10MHz—50MHzTransmitClockInputLowtTCIL0.

4T0.

5T0.

6TnsTimetCLKTPCLKInputTransitionTime0.

53nsInternaloscillatorclockfosc25MHzsource(1)Currentintodevicepinsisdefinedaspositive.

Currentoutofadevicepinisdefinedasnegative.

VoltagesarereferencedtogroundexceptVOD,ΔVOD,VTHandVTLwhicharedifferentialvoltages.

(2)Typicalvaluesrepresentmostlikelyparametricnormsat1.

8Vor3.

3V,TA=+25°C,andattheRecommendedOperationConditionsatthetimeofproductcharacterizationandarenotguaranteed.

SerializerSwitchingCharacteristics(1)(2)(3)Overrecommendedoperatingsupplyandtemperaturerangesunlessotherwisespecified.

SymbolParameterConditionsMinTypMaxUnitsCMLLow-to-HighTransitiontLHTRL=100(SeeFigure8)150330psTimeCMLHigh-to-LowTransitionRL=100tHLT150330psTime(SeeFigure8)tDISDataInputSetuptoPCLK2.

0nsSerializerDataInputs(SeeFigure14)tDIHDataInputHoldfromPCLK2.

0nsSerializerPLLLocktPLDRL=10012msTime(4)(5)RT=100f=10-50MHz6.

386T+6.

386T+tSDSerializerDelay6.

386T+5nsRegAddress0x03hb[0](TRFB=1)1219.

7(SeeFigure16)SerializeroutputintrinsicdeterministicSerializerOutputtJINDjitter.

MeasurewithPRBS-7test0.

13UI(6)DeterministicJitterpattern.

PCLK=50MHzSerializerOutputRandomSerializeroutputintrinsicrandomjittertJINR0.

04UI(6)Jitter(cycle-cycle).

Alternating–1,0pattern.

Serializeroutputpeak-to-peakjitterincludesdeterministicjitter,randomPeak-to-peakSerializertJINTjitter,andjittertransferfromserializer0.

396UI(6)OutputJitterinput.

MeasurewithPRBS-7testpattern.

SerializerJitterTransferPCLK=50MHzλSTXBW1.

9MHzFunction-3dBBandwidthDefaultRegistersSerializerJitterTransferPCLK=50MHzδSTX0.

944dBFunctionDefaultRegistersSerializerJitterTransferPCLK=50MHzδSTXf500kHzFunctionPeakingFrequencyDefaultRegisters(1)Typicalvaluesrepresentmostlikelyparametricnormsat1.

8Vor3.

3V,TA=+25°C,andattheRecommendedOperationConditionsatthetimeofproductcharacterizationandarenotguaranteed.

(2)Currentintodevicepinsisdefinedaspositive.

Currentoutofadevicepinisdefinedasnegative.

VoltagesarereferencedtogroundexceptVOD,ΔVOD,VTHandVTLwhicharedifferentialvoltages.

(3)TheElectricalCharacteristicstableslistguaranteedspecificationsunderthelistedRecommendedOperatingConditionsexceptasotherwisemodifiedorspecifiedbytheElectricalCharacteristicsConditionsand/orNotes.

Typicalspecificationsareestimationsonlyandarenotguaranteed.

(4)tPLDandtDDLTisthetimerequiredbytheserializeranddeserializertoobtaindatalockwhenexitingpower-downstatewithanactivePCLK.

(5)Specificationisguaranteedbydesignandisnottestedinproduction.

(6)UI–UnitIntervalisequivalenttooneidealserializeddatabitwidth.

TheUIscaleswithPCLKfrequency.

10SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014DeserializerSwitchingCharacteristics(1)(2)(3)(4)Overrecommendedoperatingsupplyandtemperaturerangesunlessotherwisespecified.

SymbolParameterConditionsPin/Freq.

MinTypMaxUnitstRCPReceiverOutputClockPeriodtRCP=tTCPPCLK20T100nsDefaultRegisterstPDCPCLKDutyCyclePCLK455055%SSCG[3:0]=OFFLVCMOSLow-to-HighTransitionVDDIO:1.

71Vto1.

89VortCLH1.

32.

02.

8Time3.

0Vto3.

6V,CL=8pF(lumpedload)PCLKnsLVCMOSHigh-to-LowTransitionDefaultRegisters(SeetCHL1.

32.

02.

8TimeTable1)(5)LVCMOSLow-to-HighTransitionVDDIO:1.

71Vto1.

89VortCLH1.

62.

43.

3Time3.

0Vto3.

6V,CL=8pFDeserializerData(lumpedload)nsOutputsLVCMOSHigh-to-LowTransitionDefaultRegisters(SeetCHL1.

62.

43.

3TimeTable1)(6)tROSROUTSetupDatatoPCLKVDDIO:1.

71Vto1.

89Vor0.

38T0.

5T3.

0Vto3.

6V,CL=8pFDeserializerData(lumpedload)nsOutputstROHROUTHoldDatatoPCLK0.

38T0.

5TDefaultRegisters(SeeTable1)DefaultRegisters4.

571T+4.

571T+4.

571TtDDDeserializerDelayRegister0x03hb[0]10MHz-50MHzns812+16(RRFB=1)tDDLTDeserializerDataLockTime10MHz-50MHz10mstRJITReceiverInputJitterTolerance(7)50MHz0.

53UI10MHz300550PCLKtRDJReceiverClockJitterpsSSCG[3:0]=OFF50MHz12025010MHz425600PCLKtDPJDeserializerPeriodJitter(8)psSSCG[3:0]=OFF50MHz32048010MHz320500DeserializerCycle-to-CycleClockPCLKtDCCJpsJitter(9)SSCG[3:0]=OFF50MHz300500SpreadSpectrumClocking±0.

5%tofdev20MHz-50MHz%DeviationFrequency±2.

0%LVCMOSOutputBus(SeeFigure21)SpreadSpectrumClocking±9kHztofmod20MHz-50MHzkHzModulationFrequency±66kHz(1)TheElectricalCharacteristicstableslistguaranteedspecificationsunderthelistedRecommendedOperatingConditionsexceptasotherwisemodifiedorspecifiedbytheElectricalCharacteristicsConditionsand/orNotes.

Typicalspecificationsareestimationsonlyandarenotguaranteed.

(2)Currentintodevicepinsisdefinedaspositive.

Currentoutofadevicepinisdefinedasnegative.

VoltagesarereferencedtogroundexceptVOD,ΔVOD,VTHandVTLwhicharedifferentialvoltages.

(3)Typicalvaluesrepresentmostlikelyparametricnormsat1.

8Vor3.

3V,TA=+25°C,andattheRecommendedOperationConditionsatthetimeofproductcharacterizationandarenotguaranteed.

(4)tDCJisthemaximumamountofjittermeasuredover30,000samplesbasedonTimeIntervalError(TIE).

(5)Specificationisguaranteedbycharacterizationandisnottestedinproduction.

(6)Specificationisguaranteedbydesignandisnottestedinproduction.

(7)tRJITmax(0.

61UI)islimitedbyinstrumentationandactualtRJITofin-bandjitteratlowfrequency(0100kHzfLOWSCLLowPeriod4.

7sfHIGHSCLHighPeriod4.

0sHoldtimeforastartorarepeatedstarttHD:STA4.

0sconditionSetUptimeforastartorarepeatedtSU:STA4.

7sstartconditionfSCL=100kHztHD:DATDataHoldTime03.

45stSU:DATDataSetUpTime250nstSU:STOSetUpTimeforSTOPCondition,4.

0strSCL&SDARiseTime1000nstfSCL&SDAFallTime300nsCbCapacitiveloadforbus400pFSWITCHINGCHARACTERISTICS((2))SerializerM/S=0–R/WRegister1000x05=0x40'hfSCLSCLClockFrequencykHzDeserializerM/S=0–READ100Register0x06b[6:4]=0x00'hSerializerM/S=0–R/WRegister0x05=0x40'hfLOWSCLLowPeriod4.

7μsDeserializerM/S=0–READRegister0x06b[6:4]=0x00'hSerializerM/S=0–R/WRegister0x05=0x40'hfHIGHSCLHighPeriod4.

0μsDeserializerM/S=0–READRegister0x06b[6:4]=0x00'hHoldtimeforastartorarepeatedstartSerializerM/S=0Register0x05=tHD:STA4.

0μscondition0x40'hSetUptimeforastartorarepeatedSerializerM/S=0Register0x05=μstSU:STA4.

7startcondition0x40'htHD:DATDataHoldTime03.

45μstSU:DATDataSetUpTime250nstSU:STOSetUpTimeforSTOPConditionSerializerM/S=04.

0μstfSCL&SDAFallTime300nsBusfreetimebetweenastopandstartSerializerM/S=0tBUF4.

7μsconditionSerializerM/S=11tTIMEOUTNACKTimeoutmsDeserializerMODE=125Register0x06b[2:0]=111'b(1)RecommendedInputTimingRequirementsareinputspecificationsandnottestedinproduction.

(2)Specificationisguaranteedbydesignandisnottestedinproduction.

12SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Figure6.

Bi-DirectionalControlBusTimingBi-DirectionalControlBusDCCharacteristics(SCL,SDA)-I2CCompliantSymbolParameterConditionsMinTypMaxUnits0.

7xVIHInputHighLevelSDAandSCLVDDIOVVDDIO0.

3xVILInputLowLevelVoltageSDAandSCLGNDVVDDIOVHYInputHysteresis>50mVIOZTRI-STATEOutputCurrentPDB=0VVOUT=0VorVDD-20±1+20AIINInputCurrentSDAorSCL,Vin=VDDIOorGND-20±1+20ACINInputPinCapacitance<5pFSCLandSDAVDDIO=3.

0VIOL=1.

50.

36mAVOLLowLevelOutputVoltageVSCLandSDAVDDIO=1.

71VIOL=10.

36mAACTimingDiagramsandTestCircuitsFigure7.

"WorstCase"TestPatternFigure8.

SerializerCMLOutputLoadandTransitionTimesCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback13ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comFigure9.

SerializerCMLOutputLoadandTransitionTimesFigure10.

SerializerVODDCDiagramFigure11.

SerializerVODDCDiagramFigure12.

DifferentialVTH/VTLDefinitionDiagram14SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Figure13.

SerializerInputClockTransitionTimesFigure14.

SerializerSetup/HoldTimesFigure15.

SerializerDataLockTimeFigure16.

SerializerDelayCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback15ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comFigure17.

DeserializerDataLockTimeFigure18.

DeserializerLVCMOSOutputLoadandTransitionTimesFigure19.

DeserializerDelayFigure20.

DeserializerOutputSetup/HoldTimes16SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Figure21.

SpreadSpectrumClockOutputProfileFigure22.

TypicalSerializerJitterTransferFunctionat43MHzFigure23.

TypicalDeserializerInputJitterToleranceCurveat43MHzCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback17ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTable1.

DS92LX1621ControlRegistersAddrNameBitsFieldR/WDefaultDescription(Hex)7-bitaddressofSerializer;0x58h7:1DEVICEIDRW0x58(1011_000X)default0I2CDeviceID0:DeviceIDisfromCAD0SERIDRW01:RegisterI2CDeviceIDoverridesCAD7:3RESERVED0ReservedStandbymodecontrol.

Retainscontrolregisterdata.

SupportedonlywhenM/S=00:Enabled.

Low-currentStandbymode2STANDBYRW0withwake-upcapability.

Suspendsallclocksandfunctions.

1Reset1:Disabled.

Standbyandwake-updisabled1:Resetsthedevicetodefaultregister01DIGITALRESET0RWvalues.

DoesnotaffectdeviceI2CBusorselfclearDeviceID00DIGITALRESET1RW1:DigitalReset,retainsallregistervaluesselfclear2Reserved7:0RESERVED0x20'hReservedBackChannelCRCEnable0:DisableRXCRCCRCFaultTolerant1:Enable7CHECKERRW1TransmissionForpropperCRCoperation,controlENABLEregister0x03hb[6]oftheDeserializermustbeenabled.

ForwardChannelCRCEnable0:DisableCRCFaultTolerantTXCRCGEN1:Enable6RW1TransmissionENABLEForpropperCRCoperation,controlregister0x03hb[7]oftheDeserializermustbeenabled.

AutoVDDIOdetectVDDIOControl5VDDIOCONTOLRW10:Disable1:Enable(autodetectmode)VDDIOvoltageset3OnlyusedwhenVDDIOCONTROL=0VDDIOMode4VDDIOMODERW10:1.

8V1:3.

3VI2CPass-ThroughModeI2CPASS-I2CPass-Through3RW10:DisabledTHROUGH1:EnabledReserved2RESERVED0ReservedSwitchovertointernal25MHzoscillatorclockintheabsenceofPCLKPCLK_AUTO1PCLK_AUTORW10:Disable1:EnablePixelClockEdgeSelect:0:ParallelInterfaceDataisstrobedonTRFB0TRFBRW1theFallingClockEdge.

1:ParallelInterfaceDataisstrobedontheRisingClockEdge.

7:6RESERVED01'bReserved1:CRCReset.

4CRCTransmission5CRCRESETRW0ClearsCRCErrorcounter.

4:0RESERVED0Reserved18SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Table1.

DS92LX1621ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)I2Cratioisdeterminedbythefollowing:fSCL=6.

25MHz/registervalue(indecimal)5I2CBusRate7:0I2CBUSRATERW0x400x40'h=~100kHzSCL(default)Note:Registervalues<0x32'hareNOTsupported.

DeserializerDeviceID=0x607:1DESDEVIDRW0x60(1100_000X)default6DESID0RESERVED0ReservedSLAVEDEVIDSlaveDeviceID.

Mustbeprogrammedto7:1RW0communicatewithremoteslavedevice7SlaveID0RESERVED0Reserved8Reserved7:0RESERVEDRW0Reserved9Reserved7:0RESERVEDRW1ReservedACRCErrors7:0CRCERRORB0R0NumberofCRCerrors-8LSBsBCRCErrors7:0CRCERRORB1R0NumberofCRCerrors-8MSBsReserved7:3RESERVED0Reserved1:ValidPCLKdetectedPCLKDetect2PCLKDETECTR00:ValidPCLKnotdetectedC1:CRCerrorduringcommunicationwithCRCCheck1DESERRORR0DeserializerCableLinkDetect1:Cablelinkdetected0LINKDETECTR0Status0:Cablelinknotdetected7:4RESERVED1Reserved3:2RESERVED0Reserved0:OutputDGPIO[0]Config1GPIO0DIRRW01:Input0:TRI-STATE0GPIO0ENRW11:Enabled7:4RESERVED0Reserved3:2RESERVED0Reserved0:OutputEGPIO[1]Config1GPIO1DIRRW01:Input0:TRI-STATE0GPIO1ENRW11:Enabled7:4RESERVED0Reserved3:2RESERVED0Reserved0:OutputFGPIO[2]Config1GPIO2DIRRW11:Input0:TRI-STATE0GPIO2ENRW11:Enabled7:4RESERVED0Reserved3:2RESERVED0Reserved0:Output10GPIO[3]Config1GPIO3DIRRW11:Input0:TRI-STATE0GPIO3ENRW11:Enabled7:4RESERVED0Reserved3:2RESERVED0Reserved0:Output11GPIO[4]Config1GPIO4DIRRW11:Input0:TRI-STATE0GPIO4ENRW11:EnabledCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback19ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTable1.

DS92LX1621ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)7:4RESERVED0Reserved3:2RESERVED0Reserved0:Output12GPIO[5]Config1GPIO5DIRRW11:Input0:TRI-STATE0GPIO5ENRW11:EnabledGPCR[7]GPCR[6]GPCR[5]GeneralPurposeGPCR[4]0:LOW137:0RW0ControlRegGPCR[3]1:HIGHGPCR[2]GPCR[1]GPCR[0]Table2.

DS92LX1622ControlRegistersAddrNameBitsFieldR/WDefaultDescription(Hex)7-bitaddressofDeserializer;7:1DEVICEIDRW0x60h0x60h(1100_000X)default0I2CDeviceID0:DeviceIDisfromCAD0DESIDRW01:RegisterI2CDeviceIDoverridesCAD7:3RESERVED0ReservedRemoteWake-upSelect1:Enable.

Generateremotewakeupsignalautomatically2REM_WAKEUPRW0wake-uptheSerializerinStandbymode0:Disable.

PutstheSerializer(M/S=0)inStandbymode1ResetwhenDeserializerM/S=11:Resetsthedevicetodefaultregistervalues.

Doesnot1DIGITALRESET0RW0selfclearaffectdeviceI2CBusorDeviceID0DIGITALRESET1RW0selfclear1:DigitalReset,retainsallregistervaluesReserved7:60Reserved1:OutputPCLKorInternal25MHzOscillatorclockAutoClock5AUTO_CLOCKRW00:OnlyPCLKwhenvalidPCLKpresentOutputSleepStateSelectOSSSelect4OSS_SELRW00:Outputs=TRI-STATE,whenLOCK=L1:Outputs=LOW,whenLOCK=LSSCGSelect0000:NormalOperation,SSCGOFF0001:fmod(KHz)PCLK/2168,fdev±0.

50%0010:fmod(KHz)PCLK/2168,fdev±1.

00%0011:fmod(KHz)PCLK/2168,fdev±1.

50%20100:fmod(KHz)PCLK/2168,fdev±2.

00%0101:fmod(KHz)PCLK/1300,fdev±0.

50%0110:fmod(KHz)PCLK/1300,fdev±1.

00%SSCG3:0SSCG00111:fmod(KHz)PCLK/1300,fdev±1.

50%1000:fmod(KHz)PCLK/1300,fdev±2.

00%1001:fmod(KHz)PCLK/868,fdev±0.

50%1010:fmod(KHz)PCLK/868,fdev±1.

00%1011:fmod(KHz)PCLK/868,fdev±1.

50%1100:fmod(KHz)PCLK/868,fdev±2.

00%1101:fmod(KHz)PCLK/650,fdev±0.

50%1110:fmod(KHz)PCLK/650,fdev±1.

00%1111:fmod(KHz)PCLK/650,fdev+/-1.

50%20SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Table2.

DS92LX1622ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)BackChannelCRCEnable0:DisableTxCRCCHECK7RW11:EnableENABLEForproperCRCoperation,onSerailizer0x03hb[6]CRCFaultcontrolregistermustbeEnabled.

TolerantTransmissionFowardChannelCRCEnableRxCRCGEN0:Disable6RW1ENABLE1:EnableForproperCRCoperation,onSerailizer0x03hb[7]controlregistermustbeEnabled.

AutovoltagecontrolVDDIOControl5VDDIOCONTROLRW10:Disable1:Enable(autodetectmode)VDDIOvoltagesetOnlyusedwhenVDDIOCONTROL=03VDDIOMode4VDDIOMODERW00:1.

8V1:3.

3VI2CPass-ThroughModeI2CPASS-I2CPass-Through3RW10:DisabledTHROUGH1:Enabled0:DisableAutoACK2AUTOACKRW01:EnableCRCReset1CRCRESETRW01:CRCresetPixelClockEdgeSelect0:ParallelInterfaceDataisstrobedontheFallingClockRRFB0RRFBRW1Edge1:ParallelInterfaceDataisstrobedontheRisingClockEdge.

00'h:~0.

0dB01'h:~4.

5dB03'h:~6.

5dBEQFeature07'h:~7.

5dB47:0EQRW0Control10F'h:~8.

0dB1F'h:~11.

0dB3F'h:~12.

5dBFF'h:~14.

0dB5Reserved7:0RESERVED0ReservedReserved7RESERVED0ReservedPrescalestheSCLclocklinewhenreadingdatabytefromaslavedevice(M/S=0)000:~100kHzSCL(default)001:~125kHzSCLSCLPrescale6:4SCL_PRESCALE0101:~11kHzSCL110:~33kHzSCL111:~50kHzSCLOthervaluesareNOTsupported.

RemoteNACKTimerEnableInslavemode(MODE=1)ifbitissettheI2CcorewillautomaticallytimeoutwhenREM_NACK_TIME6RemoteNACK3RW1noacknowledgeconditionwasdetected.

R1:Enable0:DisableRemoteNACKTimeout.

000:2.

0ms001:5.

2ms010:8.

6msRemoteNACK2:0NACK_TIMEOUTRW111'b011:11.

8ms100:14.

4ms101:18.

4ms110:21.

6ms111:25.

0msCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback21ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTable2.

DS92LX1622ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)SerializerDeviceID=0x587:1SERDEVIDRW0x58h(1011_000X)default7SERID0RESERVED0Reserved7:1ID[0]INDEXRW0TargetslaveDeviceIDslv_id1[7:1]8ID[0]Index0RESERVED0Reserved7:1ID[1]INDEXRW0TargetslaveDeviceIDslv_id1[7:1]9ID[1]Index0RESERVED0Reserved7:1ID[2]INDEXRW0TargetslaveDeviceIDslv_id2[7:1]AID[2]Index0RESERVED0Reserved7:1ID[3]INDEXRW0TargetslaveDeviceIDslv_id3[7:1]BID[3]Index0RESERVED0Reserved7:1ID[4]INDEXRW0TargetslaveDeviceIDslv_id4[7:1]CID[4]Index0RESERVED0Reserved7:1ID[5]INDEXRW0TargetslaveDeviceIDslv_id5[7:1]DID[5]Index0RESERVED0Reserved7:1ID[6]INDEXRW0TargetslaveDeviceIDslv_id6[7:1]EID[6]Index0RESERVED0Reserved7:1ID[7]INDEXRW0TargetslaveDeviceIDslv_id7[7:1]FID[7]Index0RESERVED0Reserved7:1ID[0]MATCHRW0AliastomatchDeviceIDslv_id0[7:1]10ID[0]Match0RESERVED0Reserved7:1ID[1]MATCHRW0AliastomatchDeviceIDslv_id1[7:1]11ID[1]Match0RESERVED0Reserved7:1ID[2]MATCHRW0AliastomatchDeviceIDslv_id2[7:1]12ID[2]Match0RESERVED0Reserved7:1ID[3]MATCHRW0AliastomatchDeviceIDslv_id3[7:1]13ID[3]Match0RESERVED0Reserved.

7:1ID[4]MATCHRW0AliastomatchDeviceIDslv_id4[7:1]14ID[4]Match0RESERVED0Reserved7:1ID[5]MATCHRW0AliastomatchDeviceIDslv_id5[7:1]15ID[5]Match0RESERVED0Reserved7:1ID[6]MATCHRW0AliastomatchDeviceIDslv_id6[7:1]16ID[6]Match0RESERVED0Reserved7:1ID[7]MATCHRW0AliastomatchDeviceIDslv_id7[7:1]17ID[7]Match0RESERVED0Reserved18Reserved7:0RESERVED0Reserved19Reserved7:0RESERVED1Reserved1ACRCErrors7:0CRCERRORB0R0NumberofCRCerrors8LSBs1BCRCErrors7:0CRCERRORB1R0NumberofCRCerrors8MSBsReserved7:3RESERVED0ReservedCRCerrorduringcommunicationwithSerializeronCRCCheck2SERERRORR0ForwardChannel1CSignalDetect0:Activesignalnotdetected1R0Status1:Activesignaldetected0:CDR/PLLUnlockedLOCKPinStatus0R01:CDR/PLLLocked22SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Table2.

DS92LX1622ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)7:3RESERVEDRW00010'bReserved1:ConfiguredasGPIO2GPIO0SETRW10:ConfiguredasROUTdata(OSS_SELcontrolled)1DGPIO[0]Config0:Output1GPIO0DIRRW11:Input0:TRI-STATE0GPIO0ENRW11:Enabled7:3RESERVEDRW0Reserved1:ConfiguredasGPIO2GPIO1SETRW10:ConfiguredasROUTdata(OSS_SELcontrolled)1EGPIO[1]Config0:Output1GPIO1DIRRW11:Input0:TRI-STATE0GPIO1ENRW11:Enabled7:3RESERVEDRW0Reserved1:ConfiguredasGPIO2GPIO2SETRW00:ConfiguredasROUT0data(OSS_SELcontrolled)1FGPIO[2]Config0:Output1GPIO2DIRRW01:Input0:TRI-STATE0GPIO2ENRW11:Enabled7:3RESERVEDRW0Reserved1:ConfiguredasGPIO2GPIO3SETRW00:ConfiguredasROUT1data(OSS_SELcontrolled)20GPIO[3]Config0:Output1GPIO3DIRRW01:Input0:Tri-state0GPIO3ENRW11:Enabled7:3RESERVEDRW0Reserved1:ConfiguredasGPIO2GPIO4SETRW00:ConfiguredasROUT2data(OSS_SELcontrolled)21GPIO[4]Config0:Output1GPIO4DIRRW01:Input0:TRI-STATE0GPIO4ENRW11:Enabled7:3RESERVEDRW0Reserved1:ConfiguredasGPIO2GPIO5SETRW00:ConfiguredasROUT3data(OSS_SELcontrolled)22GPIO[5]Config0:Output1GPIO5DIRRW01:Input0:TRI-STATE0GPIO5ENRW11:EnabledGPCR[7]GPCR[6]GPCR[5]GeneralPurposeGPCR[4]0:LOW237:0RW0ControlRegGPCR[3]1:HIGHGPCR[2]GPCR[1]GPCR[0]BISTEnable24BIST0BIST_ENRW00:Normaloperation1:BistEnable25BIST_ERR7:0BIST_ERRR0BistErrorCounterCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback23ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTable2.

DS92LX1622ControlRegisters(continued)AddrNameBitsFieldR/WDefaultDescription(Hex)11:EnableremotewakeupmodeREM_WAKEUP_E7:6RW000:NormaloperationmodeRemoteWakeN26OthervaluesareNOTsupported.

Enable5:0RESERVEDRW0Reserved0xE0:NormalOperationMode.

UsersMUSTprogram27BCC7:0BCCRW0thisvalue.

24SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014FUNCTIONALDESCRIPTIONTheDS92LX1621/DS92LX1622ChannelLinkIIIchipsetisintendedforcameraapplications.

TheSerializer/Deserializerchipsetoperatesfroma10MHzto50MHzpixelclockfrequency.

TheDS92LX1621transformsa16-bitwideparallelLVCMOSdatabusalongwithabi-directionalcontrolbusintoasinglehigh-speeddifferentialpair.

ThehighspeedserialbitstreamcontainsanembeddedclockandDC-balanceinformationwhichenhancessignalqualitytosupportACcoupling.

TheDS92LX1622receivesthesingleserialdatastreamandconvertsitbackintoa16-bitwideparalleldatabustogetherwiththebi-directionalcontrolbus.

Thebi-directionalchannelfunctionoftheDS92LX1621/DS92LX1622providesbi-directionalcommunicationbetweentheimagesensorandthehostdevice(FPGA,framegrabber,display,etc.

).

Theintegratedbackchanneltransfersdatabi-directionallyoverthesamedifferentialpairusedforvideodatainterface.

Thisinterfaceoffersadvantagesoverotherchipsetsbyeliminatingtheneedforadditionalwiresforprogrammingandcontrol.

Thebi-directionalcontrolchanneliscontrolledviaanI2Cport.

Thebi-directionalcontrolchanneloffersasynchronouscommunicationandisnotdependentonvideoblankingintervals.

SERIALFRAMEFORMATTheDS92LX1621/DS92LX1622chipsetwilltransmitandreceiveapixelofdatainthefollowingformat:Figure24.

SerialBitstreamfor28-bitSymbolTheHighSpeedForwardChannel(HS_FC)isa28-bitsymbolcomposedof16bitsofdatacontainingcameradata&controlinformationtransmittedfromSerializertoDeserializer.

CLK1andCLK0representtheembeddedclockintheserialstream.

CLK1isalwaysHIGHandCLK0isalwaysLOW.

ThisdatapayloadisoptimizedforsignaltransmissionoveranACcoupledlink.

Dataisrandomized,balancedandscrambled.

Thedatapayloadmaybecheckedusinga4-bitCRCfunction.

TheCRCmonitorsthelinkintegrityoftheserializeddataandreportswhenanerrorconditionisdetected.

Thebi-directionalcontroldataistransferredoverthesingleseriallinkalongwiththehigh-speedforwarddata.

Thisarchitectureprovidesafullduplexlowspeedforwardandbackwardpathacrosstheseriallinktogetherwithahighspeedforwardchannelwithoutthedependenceofthevideoblankingphase.

DESCRIPTIONOFBI-DIRECTIONALCONTROLBUSANDI2CMODESTheI2CcompatibleinterfaceallowsprogrammingoftheDS92LX1621,DS92LX1622,oranexternalremotedevice(suchasacamera)throughthebi-directionalcontrolchannel.

Registerprogrammingtransactionsto/fromtheDS92LX1621/DS92LX1622chipsetareemployedthroughtheclock(SCL)anddata(SDA)lines.

ThesetwosignalshaveopendrainI/Osandbothlinesmustbepulled-uptoVDDIObyexternalresistor.

Figure6showsthetimingrelationshipsoftheclock(SCL)anddata(SDA)signals.

Pull-upresistorsorcurrentsourcesarerequiredontheSCLandSDAbussestopullthemhighwhentheyarenotbeingdrivenlow.

Alogiczeroistransmittedbydrivingtheoutputlow.

Alogichighistransmittedbyreleasingtheoutputandallowingittobepulled-upexternally.

Theappropriatepull-upresistorvalueswilldependuponthetotalbuscapacitanceandoperatingspeed.

TheDS92LX1621/DS92LX1622I2Cbusdataratesupportsupto100kbpsaccordingtoI2Cspecification.

Tostartanydatatransfer,theDS92LX1621/DS92LX1622mustbeconfiguredintheproperI2Cmode.

EachdevicecanfunctionasanI2CslaveproxyormasterproxydependingonthemodedeterminedbyM/Spin.

TheSer/DesinterfaceactsasavirtualbridgebetweenMastercontroller(MCU)andtheremotedevice.

WhentheM/SpinissettoHIGH,thedeviceistreatedasaslaveproxy;actsasaslaveonbehalfoftheremoteslave.

WhenaddressingaremoteperipheralorSerializer/Deserializer(notwireddirectlytotheMCU),theslaveproxywillforwardanybytetransactionssentbytheMastercontrollertothetargetdevice.

WhenM/SpinissettoLOW,thedevicewillfunctionasamasterproxydevice;actsasamasteronbehalfoftheI2Cmastercontroller.

NotethatthedevicesmusthavecomplementarysettingsfortheM/Sconfiguration.

Forexample,iftheSerializerM/SpinissettoHIGHthentheDeserializerM/SpinmustbesettoLOWandvice-versa.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback25ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comFigure25.

WriteByteFigure26.

ReadByteFigure27.

BasicOperationFigure28.

STARTandSTOPConditionsSLAVECLOCKSTRETCHINGInordertocommunicateandsynchronizewithremotedevicesontheI2Cbusthroughthebi-directionalcontrolchannel,slaveclockstretchingmustbesupportedbytheI2Cmastercontroller/MCU.

Thechipsetutilizesbusclockstretching(holdingtheSCLlinelow)duringdatatransmission;wheretheI2CslavepullstheSCLlinelowpriortothe9thclockofeveryI2Cdatatransfer(beforetheACKsignal).

Theslavedevicewillnotcontroltheclockandonlystretchesituntiltheremoteperipheralhasresponded;whichistypicallyintheorderof12μs(typical).

26SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014CADPINADDRESSDECODERTheCADpinisusedtodecodeandsetthephysicalslaveaddressoftheSerializer/Deserializer(I2Conly)toallowuptosixdevicesonthebususingonlyasinglepin.

ThepinsetsoneofsixpossibleaddressesforeachSerializer/Deserializerdevice.

ThepinmustbepulledtoVDD(1.

8V,NOTVDDIO))witha10kresistorandapulldownresistor(RID)oftherecommendedvaluetosetthephysicaldeviceaddress.

Therecommendedmaximumresistortoleranceis0.

1%worstcase(0.

2%totaltolerance).

Figure29.

SerialControlBusConnectionTable3.

CADResistorValue-DS92LX1621SerResistorRIDAddress7'bAddress8'b0appended(WRITE)(±0.

1%)07b'1011000(h'58)8b'10110000(h'B0)GND2.

0k7b'1011001(h'59)8b'10110010(h'B2)4.

7k7b'1011010(h'5A)8b'10110100(h'B4)8.

2k7b'1011011(h'5B)8b'10110110(h'B6)12.

1k7b'1011100(h'5C)8b'10111000(h'B8)39.

0k7b'1011110(h'5E)8b'10111100(h'BC)Table4.

CADResistorValue-DS92LX1622DesResistorRIDAddress7'bAddress8'b0appended(WRITE)(±0.

1%)07b'1100000(h'60)8b'11000000(h'C0)GND2.

0k7b'1100001(h'61)8b'11000010(h'C2)4.

7k7b'1100010(h'62)8b'11000100(h'C4)8.

2k7b'1100011(h'63)8b'11010110(h'C6)12.

1k7b'1100100(h'64)8b'11011000(h'C8)39.

0k7b'1100110(h'66)8b'11001100(h'CC)CAMERAMODEOPERATIONInCameramode,I2CtransactionsoriginatefromtheMastercontrollerattheDeserializerside.

TheI2CslavecoreintheDeserializerwilldetectifatransactionisintendedfortheSerializeroraslaveattheSerializer.

Commandsaresentoverthebi-directionalcontrolchanneltoinitiatethetransactions.

TheSerializerwillreceivethecommandandgenerateanI2CtransactiononitslocalI2Cbus.

Atthesametime,theSerializerwillcapturetheresponseontheI2Cbusandreturntheresponseontheforwardchannellink.

TheDeserializerparsestheresponseandpassestheappropriateresponsetotheDeserializerI2Cbus.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback27ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comToconfigurethedevicesforcameramodeoperation,settheSerializerM/SpintoLOWandtheDeserializerM/SpintoHIGH.

BeforeinitiatinganyI2Ccommands,theDeserializerneedstobeprogrammedwiththetargetslavedeviceaddressesandSerializerdeviceaddress.

SER_DEV_IDRegister0x07hsetstheSerializerdeviceaddressandSLAVE_x_MATCH/SLAVE_x_INDEXregisters0x08h~0x17hsettheremotetargetslaveaddresses.

InslavemodetheaddressregisteriscomparedwiththeaddressbytesentbytheI2Cmaster.

Iftheaddressesareequaltoanyofregistersvalues,theI2Cslavewillacknowledgeandholdthebustopropagatethetransactiontothetargetdeviceotherwiseitreturnsnoacknowledge.

DISPLAYMODEOPERATIONInDisplaymode,I2CtransactionsoriginatefromthecontrollerattachedtotheSerializer.

TheI2CslavecoreintheSerializerwilldetectifatransactiontargets(local)registerswithintheSerialierorthe(remote)registerswithintheDeserializeroraremoteslaveconnectedtotheI2CmasterinterfaceoftheDeserializer.

Commandsaresentovertheforwardchannellinktoinitiatethetransactions.

TheDeserializerwillreceivethecommandandgenerateanI2CtransactiononitslocalI2Cbus.

Atthesametime,theDeserializerwillcapturetheresponseontheI2Cbusandreturntheresponseasacommandonthebi-directionalcontrolchannel.

TheSerializerparsestheresponseandpassestheappropriateresponsetotheSerializerI2Cbus.

ThephysicaldeviceIDoftheI2CslaveintheSerializerisdeterminedbytheanalogvoltageontheID[x]input.

ItcanbereprogrammedbyusingtheDEVICE_IDregisterandsettingthebit.

ThedeviceIDofthelogicalI2CslaveintheDeserializerisdeterminedbyprogrammingtheDESIDintheSerializer.

ThestateoftheCAD]inputontheDeserializerisusedtosetthedeviceID.

TheI2CtransactionsbetweenSer/Deswillbebridgedbetweenthehostcontrollertotheremoteslave.

Toconfigurethedevicesfordisplaymodeoperation,settheSerializerM/SpintoHIGHandtheDeserializerM/SpintoLOW.

BeforeinitiatinganyI2Ccommands,theSerializerneedstobeprogrammedwiththetargetslavedeviceaddressandSerializerdeviceaddress.

DES_DEV_IDRegister0x06hsetstheDeserializerdeviceaddressandSLAVE_DEV_IDregister0x7hsetstheremotetargetslaveaddress.

IftheI2Cslaveaddressmatchesanyofregistersvalues,theI2Cslavewillholdthetransactionallowingreadorwritetotargetdevice.

Note:InDisplaymodeoperation,registers0x08h~0x17honDeserializermustberesetto0x00.

CRC(CYCLICREDUNDANCYCHECK)A4-bitCRCpersymbolisreservedforcheckingthelinkintegrityduringtransmission.

Thereportingstatuspin(PASS)isprovidedontheDeserializerside,whichflagsanymismatchofdatatransmittedtoandfromtheremotedevice.

TheDeserializer'sPLLmustfirstbelocked(LOCKpinisHIGH)toensurethePASSstatusisvalid.

ThiserrordetectionhandlinggeneratesaninterruptsignalontothePASSoutputpin;notifyingthehostcontrollerassoonasanyerrorsareidentified.

Whenanerroroccurs,thePASSwillassertsLOW.

Anadjustableinterruptthresholdregisterisalsoavailableformanagingthedataflow.

ERRORDETECTIONTheDS92LX1621/DS92LX1622chipsetprovidesseveralerrordetectionoperationsforensuringdataintegrityinlongdistancetransmissionandreception.

Thedataerrordetectionfunctionoffersuserflexibilityandusabilityofperformingbit-by-bitanddatatransmissionerrorchecking.

Theerrordetectionoperatingmodessupportdatavalidationofthefollowingsignals:Bi-directionalControlChannelcontroldatadetectionacrossseriallinkControlVSYNCandHSYNCsignalsacrossseriallinkParallelvideo/pixeldataacrossseriallinkPROGRAMMABLECONTROLLERAnintegratedI2CslavecontrollerisembeddedineachoftheDS92LX1621SerializerandDS92LX1622Deserializer.

Itmustbeusedtoaccessandprogramtheextrafeaturesembeddedwithintheconfigurationregisters.

RefertoTable1andTable2fordetailsofcontrolregisters.

28SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014MULTIPLEDEVICEADDRESSINGSomeapplicationsrequiremultiplecameradeviceswiththesamefixedaddresstobeaccessedonthesameI2Cbus.

TheDS92LX1621/DS92LX1622provideslaveIDmatching/aliasingtogeneratedifferenttargetslaveaddresseswhenconnectingmorethantwoidenticaldevicestogetheronthesamebus.

Thisallowstheslavedevicestobeindependentlyaddressed.

EachdeviceconnectedtothebusisaddressablethroughauniqueIDbyprogrammingoftheSLAVE_ID_MATCHregisteronDeserializer.

ThiswillremaptheSLAVE_ID_MATCHaddresstothetargetSLAVE_ID_INDEXaddress;upto8IDindexesaresupported.

ThehostcontrollermustkeeptrackofthelistofI2Cperipheralsinordertoproperlyaddressthetargetdevice.

Inacameraapplication,themicrocontrollerislocatedontheDeserializerside.

Inthiscase,themicrocontrollerprogramstheslaveaddressmatchingregistersandhandlesalldatatransferstoandfromallslaveI2Cdevices.

Thisisusefulintheeventwherecameramodulesareremovedorreplaced.

ForexampleintheconfigurationshowninFigure30:Hostdevice(FPGA,framegrabber,etc.

)istheI2CmasterandhasanI2CmasterinterfaceTheI2CprotocolisbridgedfromDESAtoSERAandfromDESBtoSERBTheI2CinterfacesinSERAandSERBarebothmasterinterfacesIfthemastercontrollertransmitsI2Cslave0xA0,theDESAaddress0xE0willforwardthetransactiontoremoteCameraA.

Ifthecontrollertransmitsslaveaddress0xA2,theDESB0xE2willrecognizethat0xA2ismappedto0xA0andwillbetransmittedtotheremoteCameraB.

Ifcontrollersendscommandtoaddress0xB2,theDESB0xE2willforwardtransactiontoslavedevice0xB0.

TheSlaveIDindex/matchissupportedonlyinthecameramode(SER:M/Spin=L;DES:M/Spin=H).

ForMultipledeviceaddressingindisplaymode(SER:M/Spin=H;DES:M/Spin=L),usetheI2Cpassthroughfunction.

Figure30.

MultipleDeviceAddressingCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback29ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comI2CPASSTHROUGHI2Cpass-throughprovidesanalternativemeanstoindependentlyaddressslavedevices.

ThemodeenablesordisablesI2CbidirectionalcontrolchannelcommunicationtotheremoteI2Cbus.

ThisoptionisusedtodeterminewhetherornotanI2CinstructionistobetransferredovertotheremoteI2Cdevice.

Whenenabled,theI2CbustrafficwillcontinuetopassthroughandwillbereceivedbyI2Cdevicesdownstream.

Ifdisabled,I2CcommandswillbeblockedtotheremoteI2Cdevice.

Thepassthroughfunctionalsoprovidesaccessandcommunicationtoonlyspecificdevicesontheremotebus.

ThefeatureiseffectiveforbothCameramodeandDisplaymode.

ForexampleintheconfigurationshowninFigure31:IfmastercontrollertransmitsI2Ctransactionforaddress0xA0,theSERAwithI2CpassthroughenabledwilltransferI2CcommandstoremoteCameraA.

TheSERBwithI2Cpassthroughdisabled,anyI2CcommandswillbebypassedontheI2CbustoCameraB.

Figure31.

I2CPassThroughSYNCHRONIZINGMULTIPLECAMERASForapplicationsrequiringmultiplecamerasforframe-synchronization,itisrecommendedtoutilizetheGeneralPurposeInput/Output(GPIO)pinstotransmitcontrolsignalstosynchronizemultiplecamerastogether.

Tosynchronizethecamerasproperly,thesystemcontrollerneedstoprovideafieldsyncoutput(suchasaverticalorframesyncsignal)andthecamerasmustbesettoacceptanauxiliarysyncinput.

Theverticalsynchronizesignalcorrespondstothestartandendofaframeandthestartandendofafield.

Notethisformofsynchronizationtimingrelationshiphasanon-deterministiclatency.

Afterthecontroldataisreconstructedfromthebi-directionalcontrolchannel,therewillbeatimevariationoftheGPIOsignalsarrivingatthedifferenttargetdevices(betweentheparallellinks).

Themaximumlatencydelta(t1)oftheGPIOdatatransmittedacrossmultiplelinksis25μs.

Note:Theusermustverifythatthetimingvariationsbetweenthedifferentlinksarewithintheirsystemandtimingspecifications.

ForexampleintheconfigurationshowninFigure32:Themaximumtime(t1)betweentherisingedgeofGPIO(i.

e.

syncsignal)arrivingatCameraAandCameraBis25μs.

30SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Figure32.

SynchronizingMultipleCamerasFigure33.

GPIODeltaLatencyGENERALPURPOSEI/O(GPIO)TheDS92LX1621/DS92LX1622hasupto6GPIO(2dedicatedand4programmable).

GPIO[0]andGPIO[1]arealwaysavailableandGPIO[2:5]areavailabledependingontheparalleldatabussize.

DIN/ROUT[0:3]canbeprogrammedintoGPIOs(GPIO[2:5])whentheparalleldatabusislessthan12bitswide(10-bitdata+HS,VS).

EachGPIOcanbeconfiguredaseitheraninputoroutputport.

TheGPIOmaximumswitchingrateisupto66kHzwhenconfiguredforcommunicationbetweenDeserializerGPItoSerializerGPO.

WhereasdataflowconfiguredforcommunicationbetweenSerializerGPItoDeserializerGPOislimitedbythemaximumdatarateofthePCLK.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback31ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comAT-SPEEDBIST(BISTEN,PASS)AnoptionalATSPEEDBuiltinSelfTest(BIST)featuresupportsatspeedtestingofthehigh-speedserialandthebidirectionalcontrolchannellink.

ControlpinsattheDeserializerareusedtoenabletheBISTtestmodeandallowthesystemtoinitiatethetestandsettheduration.

AHIGHonPASSpinindicatesthatallpayloadsreceivedduringthetestwereerrorfreeduringtheBISTdurationtest.

ALOWonthispinattheconclusionofthetestindicatesthatoneormorepayloadsweredetectedwitherrors.

TheBISTdurationisdefinedbythewidthofBISTEN.

BISTstartswhenDeserializerLOCKgoesHIGHandBISTENissetHIGH.

BISTendswhenBISTENgoesLOW.

AnyerrorsdetectedaftertheBISTDurationarenotincludedinPASSlogic.

Note:AT-SPEEDBISTisonlyavailableintheCameramodeandnottheDisplaymode.

ThefollowingdiagramshowshowtoperformsystemATSPEEDBIST:Figure34.

AT-SPEEDBISTSystemFlowDiagramStep1:PlacetheDeserializerinBISTMode.

SerializerandDeserializerpowersupplymustbesupplied.

EnabletheATSPEEDBISTmodeontheDeserializerbysettingtheBISTENpinHigh.

TheDS92LX1622GPIO[1:0]pinsareusedtoselectthePCLKfrequencyoftheon-chiposcillatorfortheBISTtestonhighspeeddatapath.

Table5.

BISTOscillatorFrequencySelectDESGPIO[1:0]OscillatorSourcemin(MHz)typ(MHz)max(MHz)00ExternalPCLK105001Internal5010Internal2511Internal12.

532SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014TheDeserializerGPIO[1:0]setto00willbypasstheon-chiposcillatorandanexternaloscillatortoSerializerPCLKinputisrequired.

ThisallowstheusertooperateBISTunderdifferentfrequenciesotherthanthepredefinedranges.

Step2:EnableATSPEEDBISTbyplacingtheSerializerintoBISTmode.

Thedeserializerwillcommunicatethroughtheback-channeltoconfigureSerializerintoBISTmode.

OncetheBISTmodeisset,theSerializerwillinitiateBISTtransmissiontotheDeserializer.

Wait10msforDeserializertoacquirelockandthenmonitortheLOCKpintransitionfromLOWtoHIGH.

Atthispoint,ATSPEEDBISTisoperationalandtheBISTprocesshasbegun.

TheSerializerwillstarttransferofaninternallygeneratedPRBSdatapatternthroughthehighspeedseriallink.

ThispatterntraversesacrosstheinterconnectinglinktotheDeserializer.

CheckthestatusofthePASSpin;aHIGHindicatesapass,aLOWindicatesafail.

AfailwillstayLOWforaclockcycle.

IftwoormorebitsfailinarowthePASSpinwilltoggleclockcycleHIGHandclockcyclelow.

TheusercanusethePASSpintocountthenumberoffailsonthehighspeedlink.

Inaddition,thereisadefinedSERandDESregisterthatwillkeeptrackoftheaccumulatederrorcount.

TheSerializerDS92LX1621GPIO[0]pinwillbeassignedasaPASSflagerrorindicatorforthebi-directionalcontrolchannellink.

Figure35.

BISTTimingDiagramStep3:StopatSPEEDBISTbyturningoffBISTmodeintheDeserializertodeterminePass/Fail.

ToendBIST,thesystemmustpullBISTENpinoftheDeserializerLOW.

TheBISTdurationisfullydefinedbytheBISTENwidthandthustheBitErrorRateisdeterminedbyhowlongthesystemholdsBISTENHIGH.

Figure36.

BISTBERCalculationCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback33ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comForinstance,ifBISTENisheldHIGHfor1secondandthePCLKisrunningat43MHzwith16bpp,thentheBitErrorRateisnobetterthan1.

46E-9.

Step4:PlacesysteminNormalOperatingModebydisablingBISTattheSerializer.

OnceStep3iscomplete,ATSPEEDBISTisoverandtheDeserializerisoutofBISTmode.

TofullyreturntoNormalmode,applyNormalinputdataintotheSerializer.

AnyPASSresultwillremainunlessitischangedbyanewBISTsessionorclearedbyassertingandreleasingPDB.

ThedefaultstateofPASSafteraPDBtoggleisHIGH.

ItisimportanttonotethatATSPEEDBISTwillonlydetermineifthereisanissueonthelinkthatisnotrelatedtotheclockanddatarecoveryofthelink(whosestatusisflaggedwithLOCKpin).

LVCMOSVDDIOOPTION1.

8Vor3.

3VSERInputsandDESOutputsareuserconfigurabletoprovidecompatibilitywith1.

8Vand3.

3Vsysteminterfaces.

REMOTEWAKEUP(CameraMode)Afterinitialpowerup,theSERisinalow-powerStandbymode.

TheDES(controlledbyhostcontroller)'RemoteWake-up'registerallowstheDESsidetogenerateasignalacrossthelinktoremotelywake-uptheSER.

OncetheSERdetectsthewake-upsignal,theSERswitchesfromStandbymodetoactivemode.

Inactivemode,theSERlocksontoPCLKinput(ifpresent),otherwisetheon-chiposcillatorisusedastheinputclocksource.

NotethehostcontrollershouldmonitortheDESLOCKpinandconfirmLOCK=HbeforeperforminganyI2Ccommunicationacrossthelink.

ForRemoteWake-uptofunctionproperly:ThechipsetneedstobeconfiguredinCameramode:SERM/S=0andDESM/S=1TheSERexpectsremotewake-upbydefaultatpoweron.

ConfigurethecontrolchanneldriveroftheDEStobeinremotewakeupmodebysettingDESregister0x26to0xC0.

PerformremotewakeuponSERbysettingDESregister0x01b[2]to1.

ReturnthecontrolchanneldriveroftheDEStothenormaloperationmodebysettingDESregister0x26to0.

TheSERcanalsobeputintostandbymodebyprogrammingtheDESremotewakeupcontrolregister0x01b[2]REM_WAKEUPto0.

POWERDOWNTheSERhasaPDBinputpintoENABLEorPowerdownthedevice.

Themodescanbecontrolledbythehostandisusedtodisablethelinktosavepowerwhentheremotedeviceisnotoperational.

Anautomodeisalsoavailable.

Inthismode,thePDBpinistiedHIGHandtheSERswitchesovertoaninternaloscillatorwhenthePCLKstopsornotpresent.

WhenaPCLKstartsagain,theSERwillthenlocktothevalidinputPCLKandtransmitsthedatatotheDES.

Inpowerdownmode,thehigh-speeddriveroutputsarestatic(HIGH).

TheDEShasaPDBinputpintoENABLEorPowerdownthedevice.

ThispincanbecontrolledbythesystemandisusedtodisabletheDEStosavepower.

Anautomodeisalsoavailable.

Inthismode,thePDBpinistiedHIGHandtheDESwillenterpowerdownwhentheserialstreamstops.

Whentheserialstreamstartsupagain,theDESwilllocktotheinputstreamandasserttheLOCKpinandoutputvaliddata.

Inpowerdownmode,theDataandPCLKoutputsaresetbytheOSS_SELcontrolregister.

POWERUPREQUIREMENTSANDPDBPINItisrequiredtodelayandreleasethePDBinputsignalafterVDD(VDDnandVDDIO)powersupplieshavesettledtotherecommendedoperatingvoltages.

AexternalRCnetworkcanbeconnectedtothePDBpintoensurePDBarrivesafteralltheVDDhavestabilized.

34SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014SIGNALQUALITYENHANCERSDes-ReceiverInputEqualization(EQ)Thereceiverinputsprovidedinputequalizationfilterinordertocompensateforlossfromthemedia.

Thelevelofequalizationiscontrolledviaregistersetting.

EMIREDUCTIONDes-ReceiverStaggeredOutputTheReceiverstaggeredoutputsallowsforoutputstoswitchinarandomdistributionoftransitionswithinadefinedwindow.

Outputstransitionsaredistributedrandomly.

Thisminimizesthenumberofoutputsswitchingsimultaneouslyandhelpstoreducesupplynoise.

InadditionitspreadsthenoisespectrumoutreducingoverallEMI.

DesSpreadSpectrumClockingCompatibiltyTheDS92LX1622paralleldataandclockoutputshaveprogrammableSSCGrangesfrom9kHz–66kHzand±0.

5%–±2%from20MHzto50MHz.

ThemodulationrateandmodulationfrequencyvariationofoutputspreadiscontrolledthroughtheSSCcontrolregisters.

PIXELCLOCKEDGESELECT(TRFB/RRFB)TheTRFB/RRFBselectswhichedgeofthePixelClockisused.

FortheSER,thisregisterdeterminestheedgethatthedataislatchedon.

IfTRFBregisteris1,dataislatchedontheRisingedgeofthePCLK.

IfTRFBregisteris0,dataislatchedontheFallingedgeofthePCLK.

FortheDES,thisregisterdeterminestheedgethatthedataisstrobedon.

IfRRFBregisteris1,dataisstrobedontheRisingedgeofthePCLK.

IfRRFBregisteris0,dataisstrobedontheFallingedgeofthePCLK.

Figure37.

ProgrammablePCLKStrobeSelectApplicationsInformationACCOUPLINGTheSER/DESsupportsonlyAC-coupledinterconnectsthroughanintegratedDCbalanceddecodingscheme.

TousethedeviceinanAC-coupledapplication,insertexternalACcouplingcapacitorsinseriesintheChannelLinkIIIsignalpathasillustratedinFigure38.

Figure38.

AC-CoupledApplicationForhigh-speedChannelLinkIIItransmissions,thesmallestavailablepackageshouldbeusedfortheACcouplingcapacitor.

Thiswillhelpminimizedegradationofsignalqualityduetopackageparasitics.

Themostcommonusedcapacitorvaluefortheinterfaceis0.

1μF.

TYPICALAPPLICATIONCONNECTIONFigure39showsatypicalconnectionoftheDS92LX1621Serializer.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback35ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comFigure39.

DS92LX1621TypicalConnectionDiagram36SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014Figure40showsatypicalconnectionoftheDS92LX1622Deserializer.

Figure40.

DS92LX1622TypicalConnectionDiagramCopyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback37ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comTRANSMISSIONMEDIATheSer/Deschipsetisintendedtobeusedoverawidevarietyofbalancedcablesdependingondistanceandsignalqualityrequirements.

TheSer/Desemployinternalterminationprovidingacleansignalingenvironment.

TheinterconnectforChannelLinkIIIinterfaceshouldpresentadifferentialimpedanceof100Ohms.

Useofcablesandconnectorsthathavematcheddifferentialimpedancewillminimizeimpedancediscontinuities.

Shieldedorun-shieldedcablesmaybeuseddependinguponthenoiseenvironmentandapplicationrequirements.

Thechipset'soptimumcabledriveperformanceisachievedat43MHzat10meterslength.

Themaximumsignalingrateincreasesasthecablelengthdecreases.

Therefore,thechipsetsupports50MHzatshorterdistances.

Othercableparametersthatmaylimitthecable'sperformanceboundariesare:cableattenuation,near-endcrosstalkandintra-pairskew.

Forobtainingoptimalperformance,thefollowingisrecommended:UseShieldedTwistedPair(STP)cable100±10%differentialimpedanceand24AWG(orlowerAWG)cableLowintra-pairskew(lessthan0.

1UI),impedancematchedTerminateunusedconductorsOptimumsettingsfordeserializerRegister0x27(SeeTable2)PCBLAYOUTANDPOWERSYSTEMCONSIDERATIONSCircuitboardlayoutandstack-upfortheSer/Desdevicesshouldbedesignedtoprovidelow-noisepowerfeedtothedevice.

Goodlayoutpracticewillalsoseparatehighfrequencyorhigh-levelinputsandoutputstominimizeunwantedstraynoisepickup,feedbackandinterference.

Powersystemperformancemaybegreatlyimprovedbyusingthindielectrics(2to4mils)forpower/groundsandwiches.

ThisarrangementprovidesplanecapacitanceforthePCBpowersystemwithlow-inductanceparasitics,whichhasprovenespeciallyeffectiveathighfrequencies,andmakesthevalueandplacementofexternalbypasscapacitorslesscritical.

ExternalbypasscapacitorsshouldincludebothRFceramicandtantalumelectrolytictypes.

RFcapacitorsmayusevaluesintherangeof0.

01uFto0.

1uF.

Tantalumcapacitorsmaybeinthe2.

2uFto10uFrange.

Voltageratingofthetantalumcapacitorsshouldbeatleast5Xthepowersupplyvoltagebeingused.

Surfacemountcapacitorsarerecommendedduetotheirsmallerparasitics.

Whenusingmultiplecapacitorspersupplypin,locatethesmallervalueclosertothepin.

Alargebulkcapacitorisrecommendatthepointofpowerentry.

Thisistypicallyinthe50uFto100uFrangeandwillsmoothlowfrequencyswitchingnoise.

Itisrecommendedtoconnectpowerandgroundpinsdirectlytothepowerandgroundplaneswithbypasscapacitorsconnectedtotheplanewithviaonbothendsofthecapacitor.

Connectingpowerorgroundpinstoanexternalbypasscapacitorwillincreasetheinductanceofthepath.

AsmallbodysizeX7Rchipcapacitor,suchas0603,isrecommendedforexternalbypass.

Itssmallbodysizereducestheparasiticinductanceofthecapacitor.

Theusermustpayattentiontotheresonancefrequencyoftheseexternalbypasscapacitors,usuallyintherangeof20-30MHz.

Toprovideeffectivebypassing,multiplecapacitorsareoftenusedtoachievelowimpedancebetweenthesupplyrailsoverthefrequencyofinterest.

Athighfrequency,itisalsoacommonpracticetousetwoviasfrompowerandgroundpinstotheplanes,reducingtheimpedanceathighfrequency.

Somedevicesprovideseparatepowerfordifferentportionsofthecircuit.

Thisisdonetoisolateswitchingnoiseeffectsbetweendifferentsectionsofthecircuit.

SeparateplanesonthePCBaretypicallynotrequired.

PinDescriptiontablestypicallyprovideguidanceonwhichcircuitblocksareconnectedtowhichpowerpinpairs.

Insomecases,anexternalfiltermanybeusedtoprovidecleanpowertosensitivecircuitssuchasPLLs.

Useatleastafourlayerboardwithapowerandgroundplane.

LocateLVCMOSsignalsawayfromthedifferentiallinestopreventcouplingfromtheLVCMOSlinestothedifferentiallines.

Closely-coupleddifferentiallinesof100Ohmsaretypicallyrecommendedfordifferentialinterconnect.

Thecloselycoupledlineshelptoensurethatcouplednoisewillappearascommon-modeandthusisrejectedbythereceivers.

Thetightlycoupledlineswillalsoradiateless.

InformationontheLLPstylepackageisprovidedintheAN-1187LeadlessLeadframePackage(LLP)ApplicationReport(literaturenumberSNOA401).

38SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622www.

ti.

comSNLS327I–MAY2010–REVISEDJANUARY2014INTERCONNECTGUIDELINESForfulldetails,seetheChannel-LinkPCBandInterconnectDesign-InGuidelines(literaturenumberSNLA008)andtheTransmissionLineRAPIDESIGNEROperationandApplicationsGuide(literaturenumberSNLA035).

Use100coupleddifferentialpairsUsetheS/2S/3Sruleinspacings–S=spacebetweenthepair–2S=spacebetweenpairs–3S=spacetoLVCMOSsignalMinimizethenumberofViasUsedifferentialconnectorswhenoperatingabove500MbpslinespeedMaintainbalanceofthetracesMinimizeskewwithinthepairAdditionalgeneralguidancecanbefoundintheLVDSOwner'sManual(literaturenumberSNLA187),whichisavailableinPDFformatfromtheTILVDS&CMLSolutionswebsite.

Copyright2010–2014,TexasInstrumentsIncorporatedSubmitDocumentationFeedback39ProductFolderLinks:DS92LX1621DS92LX1622DS92LX1621,DS92LX1622SNLS327I–MAY2010–REVISEDJANUARY2014www.

ti.

comREVISIONHISTORYChangesfromRevisionH(April2013)toRevisionIPageChanged"tri-state"and"low"OSSvaluestoreflectcorrectbitdefinition20Addeduser-recommendedvaluefordeserializerechocancellationingeneral-purposecables24Addedtolerancefortransmissioncableimpedance38Addedtolerancerangefortransmissioncableskew38AddedreferencetooptimumsettingsinformationindeserializerReg0x2738ChangesfromRevisionG(April2013)toRevisionHPageChangedlayoutofNationalDataSheettoTIformat3940SubmitDocumentationFeedbackCopyright2010–2014,TexasInstrumentsIncorporatedProductFolderLinks:DS92LX1621DS92LX1622PACKAGEOPTIONADDENDUMwww.

ti.

com10-Dec-2020Addendum-Page1PACKAGINGINFORMATIONOrderableDeviceStatus(1)PackageTypePackageDrawingPinsPackageQtyEcoPlan(2)Leadfinish/Ballmaterial(6)MSLPeakTemp(3)OpTemp(°C)DeviceMarking(4/5)SamplesDS92LX1621SQ/NOPBACTIVEWQFNRTV321000RoHS&GreenSNLevel-3-260C-168HR-40to85LX1621DS92LX1621SQE/NOPBACTIVEWQFNRTV32250RoHS&GreenSNLevel-3-260C-168HR-40to85LX1621DS92LX1621SQX/NOPBACTIVEWQFNRTV324500RoHS&GreenSNLevel-3-260C-168HR-40to85LX1621DS92LX1622SQ/NOPBACTIVEWQFNRTA401000RoHS&GreenSNLevel-3-260C-168HR-40to85LX1622DS92LX1622SQE/NOPBACTIVEWQFNRTA40250RoHS&GreenSNLevel-3-260C-168HR-40to85LX1622DS92LX1622SQX/NOPBACTIVEWQFNRTA402500RoHS&GreenSNLevel-3-260C-168HR-40to85LX1622(1)Themarketingstatusvaluesaredefinedasfollows:ACTIVE:Productdevicerecommendedfornewdesigns.

LIFEBUY:TIhasannouncedthatthedevicewillbediscontinued,andalifetime-buyperiodisineffect.

NRND:Notrecommendedfornewdesigns.

Deviceisinproductiontosupportexistingcustomers,butTIdoesnotrecommendusingthispartinanewdesign.

PREVIEW:Devicehasbeenannouncedbutisnotinproduction.

Samplesmayormaynotbeavailable.

OBSOLETE:TIhasdiscontinuedtheproductionofthedevice.

(2)RoHS:TIdefines"RoHS"tomeansemiconductorproductsthatarecompliantwiththecurrentEURoHSrequirementsforall10RoHSsubstances,includingtherequirementthatRoHSsubstancedonotexceed0.

1%byweightinhomogeneousmaterials.

Wheredesignedtobesolderedathightemperatures,"RoHS"productsaresuitableforuseinspecifiedlead-freeprocesses.

TImayreferencethesetypesofproductsas"Pb-Free".

RoHSExempt:TIdefines"RoHSExempt"tomeanproductsthatcontainleadbutarecompliantwithEURoHSpursuanttoaspecificEURoHSexemption.

Green:TIdefines"Green"tomeanthecontentofChlorine(Cl)andBromine(Br)basedflameretardantsmeetJS709Blowhalogenrequirementsof<=1000ppmthreshold.

Antimonytrioxidebasedflameretardantsmustalsomeetthe<=1000ppmthresholdrequirement.

(3)MSL,PeakTemp.

-TheMoistureSensitivityLevelratingaccordingtotheJEDECindustrystandardclassifications,andpeaksoldertemperature.

(4)Theremaybeadditionalmarking,whichrelatestothelogo,thelottracecodeinformation,ortheenvironmentalcategoryonthedevice.

(5)MultipleDeviceMarkingswillbeinsideparentheses.

OnlyoneDeviceMarkingcontainedinparenthesesandseparatedbya"~"willappearonadevice.

IfalineisindentedthenitisacontinuationofthepreviouslineandthetwocombinedrepresenttheentireDeviceMarkingforthatdevice.

(6)Leadfinish/Ballmaterial-OrderableDevicesmayhavemultiplematerialfinishoptions.

Finishoptionsareseparatedbyaverticalruledline.

Leadfinish/Ballmaterialvaluesmaywraptotwolinesifthefinishvalueexceedsthemaximumcolumnwidth.

PACKAGEOPTIONADDENDUMwww.

ti.

com10-Dec-2020Addendum-Page2ImportantInformationandDisclaimer:TheinformationprovidedonthispagerepresentsTI'sknowledgeandbeliefasofthedatethatitisprovided.

TIbasesitsknowledgeandbeliefoninformationprovidedbythirdparties,andmakesnorepresentationorwarrantyastotheaccuracyofsuchinformation.

Effortsareunderwaytobetterintegrateinformationfromthirdparties.

TIhastakenandcontinuestotakereasonablestepstoproviderepresentativeandaccurateinformationbutmaynothaveconducteddestructivetestingorchemicalanalysisonincomingmaterialsandchemicals.

TIandTIsuppliersconsidercertaininformationtobeproprietary,andthusCASnumbersandotherlimitedinformationmaynotbeavailableforrelease.

InnoeventshallTI'sliabilityarisingoutofsuchinformationexceedthetotalpurchasepriceoftheTIpart(s)atissueinthisdocumentsoldbyTItoCustomeronanannualbasis.

TAPEANDREELINFORMATION*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQReelDiameter(mm)ReelWidthW1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W(mm)Pin1QuadrantDS92LX1621SQ/NOPBWQFNRTV321000178.

012.

45.

35.

31.

38.

012.

0Q1DS92LX1621SQE/NOPBWQFNRTV32250178.

012.

45.

35.

31.

38.

012.

0Q1DS92LX1621SQX/NOPBWQFNRTV324500330.

012.

45.

35.

31.

38.

012.

0Q1DS92LX1622SQ/NOPBWQFNRTA401000330.

016.

46.

36.

31.

512.

016.

0Q1DS92LX1622SQE/NOPBWQFNRTA40250178.

016.

46.

36.

31.

512.

016.

0Q1DS92LX1622SQX/NOPBWQFNRTA402500330.

016.

46.

36.

31.

512.

016.

0Q1PACKAGEMATERIALSINFORMATIONwww.

ti.

com24-May-2017PackMaterials-Page1*AlldimensionsarenominalDevicePackageTypePackageDrawingPinsSPQLength(mm)Width(mm)Height(mm)DS92LX1621SQ/NOPBWQFNRTV321000210.

0185.

035.

0DS92LX1621SQE/NOPBWQFNRTV32250210.

0185.

035.

0DS92LX1621SQX/NOPBWQFNRTV324500367.

0367.

035.

0DS92LX1622SQ/NOPBWQFNRTA401000367.

0367.

038.

0DS92LX1622SQE/NOPBWQFNRTA40250210.

0185.

035.

0DS92LX1622SQX/NOPBWQFNRTA402500367.

0367.

038.

0PACKAGEMATERIALSINFORMATIONwww.

ti.

com24-May-2017PackMaterials-Page2www.

ti.

comPACKAGEOUTLINEC5.

154.

855.

154.

850.

80.

70.

050.

002X3.

528X0.

52X3.

532X0.

50.

332X0.

300.

183.

10.

1(0.

1)TYPWQFN-0.

8mmmaxheightRTV0032APLASTICQUADFLATPACK-NOLEAD4224386/B04/20190.

08C0.

1CAB0.

05NOTES:1.

Alllineardimensionsareinmillimeters.

Anydimensionsinparenthesisareforreferenceonly.

DimensioningandtolerancingperASMEY14.

5M.

2.

Thisdrawingissubjecttochangewithoutnotice.

3.

Thepackagethermalpadmustbesolderedtotheprintedcircuitboardforthermalandmechanicalperformance.

PIN1INDEXAREASEATINGPLANEPIN1IDSYMMEXPOSEDTHERMALPADSYMM189161724253233SCALE2.

500ABwww.

ti.

comEXAMPLEBOARDLAYOUT28X(0.

5)(1.

3)(1.

3)(R0.

05)TYP0.

07MAXALLAROUND0.

07MINALLAROUND32X(0.

6)32X(0.

24)(4.

8)(4.

8)(3.

1)(3.

1)(0.

2)TYPVIAWQFN-0.

8mmmaxheightRTV0032APLASTICQUADFLATPACK-NOLEAD4224386/B04/2019NOTES:(continued)4.

Thispackageisdesignedtobesolderedtoathermalpadontheboard.

Formoreinformation,seeTexasInstrumentsliteraturenumberSLUA271(www.

ti.

com/lit/slua271).

5.

Viasareoptionaldependingonapplication,refertodevicedatasheet.

Ifanyviasareimplemented,refertotheirlocationsshownonthisview.

Itisrecommendedthatviasunderpastebefilled,pluggedortented.

SYMMSYMMSEESOLDERMASKDETAILLANDPATTERNEXAMPLEEXPOSEDMETALSHOWNSCALE:15X189161724253233METALEDGESOLDERMASKOPENINGEXPOSEDMETALMETALUNDERSOLDERMASKSOLDERMASKOPENINGEXPOSEDMETALNONSOLDERMASKDEFINED(PREFERRED)SOLDERMASKDEFINEDSOLDERMASKDETAILSwww.

ti.

comEXAMPLESTENCILDESIGN32X(0.

6)32X(0.

24)28X(0.

5)(4.

8)(4.

8)(0.

775)TYP(0.

775)TYP4X(1.

35)4X(1.

35)(R0.

05)TYPWQFN-0.

8mmmaxheightRTV0032APLASTICQUADFLATPACK-NOLEAD4224386/B04/2019NOTES:(continued)6.

Lasercuttingapertureswithtrapezoidalwallsandroundedcornersmayofferbetterpasterelease.

IPC-7525mayhavealternatedesignrecommendations.

SOLDERPASTEEXAMPLEBASEDON0.

125MMTHICKSTENCILSCALE:20XEXPOSEDPAD3376%PRINTEDSOLDERCOVERAGEBYAREAUNDERPACKAGESYMMSYMM189161724253233www.

ti.

comPACKAGEOUTLINECSEETERMINALDETAIL40X0.

30.

24.

60.

140X0.

50.

30.

8MAX(0.

1)TYP0.

050.

0036X0.

54X4.

5A6.

15.

9B6.

15.

90.

50.

30.

30.

2(0.

2)TYPWQFN-0.

8mmmaxheightRTA0040APLASTICQUADFLATPACK-NOLEAD4214989/B02/2017PIN1INDEXAREA0.

08SEATINGPLANE110213011204031(OPTIONAL)PIN1ID0.

1CAB0.

05EXPOSEDTHERMALPADNOTES:1.

Alllineardimensionsareinmillimeters.

Anydimensionsinparenthesisareforreferenceonly.

DimensioningandtolerancingperASMEY14.

5M.

2.

Thisdrawingissubjecttochangewithoutnotice.

3.

Thepackagethermalpadmustbesolderedtotheprintedcircuitboardforthermalandmechanicalperformance.

SCALE2.

200DETAILOPTIONALTERMINALTYPICALwww.

ti.

comEXAMPLEBOARDLAYOUT0.

07MINALLAROUND0.

07MAXALLAROUND40X(0.

25)40X(0.

6)(0.

2)TYPVIA36X(0.

5)(5.

8)(5.

8)(4.

6)(R0.

05)TYP(0.

74)TYP(1.

31)TYP(0.

74)TYP(1.

31TYP)WQFN-0.

8mmmaxheightRTA0040APLASTICQUADFLATPACK-NOLEAD4214989/B02/2017SYMM110112021303140SYMMLANDPATTERNEXAMPLEEXPOSEDMETALSHOWNSCALE:12XNOTES:(continued)4.

Thispackageisdesignedtobesolderedtoathermalpadontheboard.

Formoreinformation,seeTexasInstrumentsliteraturenumberSLUA271(www.

ti.

com/lit/slua271).

5.

Viasareoptionaldependingonapplication,refertodevicedatasheet.

Ifanyviasareimplemented,refertotheirlocationsshownonthisview.

Itisrecommendedthatviasunderpastebefilled,pluggedortented.

SOLDERMASKOPENINGMETALUNDERSOLDERMASKSOLDERMASKDEFINEDEXPOSEDMETALMETALSOLDERMASKOPENINGSOLDERMASKDETAILSNONSOLDERMASKDEFINED(PREFERRED)EXPOSEDMETALwww.

ti.

comEXAMPLESTENCILDESIGN40X(0.

6)40X(0.

25)36X(0.

5)(5.

8)(5.

8)9X(1.

28)(1.

48)TYP(R0.

05)TYP(1.

48)TYPWQFN-0.

8mmmaxheightRTA0040APLASTICQUADFLATPACK-NOLEAD4214989/B02/2017NOTES:(continued)6.

Lasercuttingapertureswithtrapezoidalwallsandroundedcornersmayofferbetterpasterelease.

IPC-7525mayhavealternatedesignrecommendations.

SYMMMETALTYPSOLDERPASTEEXAMPLEBASEDON0.

125mmTHICKSTENCILEXPOSEDPAD70%PRINTEDSOLDERCOVERAGEBYAREASCALE:15XSYMM110112021303140IMPORTANTNOTICEANDDISCLAIMERTIPROVIDESTECHNICALANDRELIABILITYDATA(INCLUDINGDATASHEETS),DESIGNRESOURCES(INCLUDINGREFERENCEDESIGNS),APPLICATIONOROTHERDESIGNADVICE,WEBTOOLS,SAFETYINFORMATION,ANDOTHERRESOURCES"ASIS"ANDWITHALLFAULTS,ANDDISCLAIMSALLWARRANTIES,EXPRESSANDIMPLIED,INCLUDINGWITHOUTLIMITATIONANYIMPLIEDWARRANTIESOFMERCHANTABILITY,FITNESSFORAPARTICULARPURPOSEORNON-INFRINGEMENTOFTHIRDPARTYINTELLECTUALPROPERTYRIGHTS.

TheseresourcesareintendedforskilleddevelopersdesigningwithTIproducts.

Youaresolelyresponsiblefor(1)selectingtheappropriateTIproductsforyourapplication,(2)designing,validatingandtestingyourapplication,and(3)ensuringyourapplicationmeetsapplicablestandards,andanyothersafety,security,orotherrequirements.

Theseresourcesaresubjecttochangewithoutnotice.

TIgrantsyoupermissiontousetheseresourcesonlyfordevelopmentofanapplicationthatusestheTIproductsdescribedintheresource.

Otherreproductionanddisplayoftheseresourcesisprohibited.

NolicenseisgrantedtoanyotherTIintellectualpropertyrightortoanythirdpartyintellectualpropertyright.