并行加法器求四位全加器原理!?

并行加法器 时间:2021-08-12 阅读:()

如何用一位全加器设计4位串行进行二进制并行加法器?

加法器是基于二进制逻辑关系5261设计的。假设计算的是 a1+a2,和为4102c[1:0],有下列两种关系: 1. a1和a2都为1时,进位c[1]=1,即逻辑与1653; 2. a1和a2只有一个为1时,低位c[0]=1,即逻辑异或回; 因此加法器的实现方式为答 c[1]=a1 and a2, c[0]=a1 xor a2 。

超前进位加法器原理

超前进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通全加器串联时互相进位产生的延迟进行了改良。超前进位加法器是通过增加了一个不是十分复杂的逻辑电路来做到这点的。

全加器的工作原理

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

多个一位全加器进行级联可以得到多位全加器。

常用二进制四位全加器74LS283。

一位全加器(FA)的逻辑表达式为: S=A?B?Cin;Cout=AB+BCin+ACin,其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;如果要实现多位加法可以进行级联,就是串起来使用。

比如32位+32位,就需要32个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法。

如果将全加器的输入置换成A和B的组合函数Xi和Y(S0…S3控制),然后再将X,Y和进位数通过全加器进行全加,就是ALU的逻辑结构结构。

即 X=f(A,B);Y=f(A,B)不同的控制参数可以得到不同的组合函数,因而能够实现多种算术运算和逻辑运算。

扩展资料: 有了全加器,构造加法器就非常容易了,假设有A3A2A1A0和B3B2B1B0,利用全加器构造A3A2A1A0+B3B2B1B0的串行进位加法器电路图。

其中C-1=0,因为已是最低位,没有进位。

这种串联方法只是完成了基本功能,从效率上则完全不可行。

假设全加器中每个元器件的时延为t,则全加器的时延为2t(见全加器电路图),对于4位加法器,按照这种串联方法,加法器构造方法1中图中最右边(最低位)全加器计算完成后,才能计算右二个全加器,以此类推。

因此,4位加法器至少需要4*2t=8t的时延;如果是32位,则是64t的时延。

显然,这种加法器的效率与参与计算的二进数长度成正比,数越长,时延越长。

在现代计算机中,是不可能采用如此低效的加法器的。

只需要把Ci和参与运算的两个4位二进制数之间的关系梳理清楚就行了。

直接用代入法展开得: 在这个关系式里,直接列出了4位二进制加法的最终进位,不用等待低位计算完了,再计算高位,而是直接进行计算,最终得到的超前进位加法器电路图。

假设超前进位加法器中的每个门时延是t,对于4位加法,最多经过4t的时延,而且,即使增加更多的位数,其时延也是4t。

对比串行进位加法器和超前进位加法器,前者线路简单,时延与参与计算的二进制串长度成正比,而后者则是线路复杂,时延是固定值。

通常,对于32的二进制串,可以对其进行分组,每8位一组,组内加法用超前进位加法器,组间进位则用串行进位。

采用这种折中方法,既保证了效率,又降低了内部线路复杂度。

参考资料来源:搜狗百科-全加器

什么叫低位来的进位?数电。。。

我们平时常用的都是10进制,满10进1,也就是当低位的值够10之后,就在高位上加1,本位变成0。2进制就是同理,计数时满2进1,当低位满2之后,就在高位+1,低位变成0。

具体,以10进制和2进制的对比来看: 十进制---二进制 0 --- 0 1 --- 1 2 --- 10 低位满2,向高位进1,低位归0后面也是一次类推。

3 --- 11 4 --- 100 需要注意的是,对于100这个数字来说,如果不特别说明,我们肯定认为这是10进制,也就是一百如果特别注明这个数是2进制,则这个数代表的就是4。

对于1+1+1+1来说,简单来看(2进制)就是1+1+1+1=((1+1)+1)+1=(10+1)+1=11+1=100。

扩展资料 并行加法器由多个全加器组成,其位数的多少取决于机器的字长,数据的各位同时运算。

并行加法器虽然操作数的各位是同时提供的,但低位运算所产生的进位有可能会影响高位的运算结果。

例如:11…11和00…01相加,最低位产生的进位将逐位影响至最高位。

因此,并行加法器的最长运算时间主要是由进位信号的传递时间决定的。

提高并行加法器速度的关键是尽量加快进位产生和传递的速度 。

进位表达式:Ci=AiBi+(Ai?Bi)Ci-1 Gi的含义是:若本位的两个输入均为1,必然要向高位产生进位。

?Pi的含义是:当两个输入中有一个为1,低位传来的进位Ci-1将超越本位向更高的位传送。

参考资料来源:百度百科-二进制进位

如何用四个全加器构成4位并行进位加法器

用74LS283芯片和74LS86芯片通过拨码开关来控制高低电平作为二进制的0和1,用普通led灯来展现高低电平状态,高电平则灯亮,低电平则灯灭,通过2位的拨码开关来实现加法器和减法器的转换,经过两组芯片后电流通过led,led灯亮,则表示为1,如果灯灭,则表示为0,设计一个电源电路,将9v的交流电压降到5v,再输入到加法器、减法器电路,能够实现8位的二进制相加或则相减,结果的范围应该在00000000到111111110之间,八位二进制数换算成三位十进制数最大为255。通过86芯片的与非门,实现逢八进一,然后将74823芯片进行串联实现8位数相加减,超前进位并行加法器74LS283可以实现四位二进制数的相加,需要两个74LS283进行串联,这样就得到一个新的8位二进制数,其范围在000到510之间。

实现4位并行进位加法器。

扩展资料 逻辑优化 逻辑优化设计的主要目的是减少信号的翻转活动,它通过将电路的逻辑功能尽可能的分解、优化, 减少逻辑深度,减少信号假翻转,从而使翻转活动最小,减小电路的功耗。

令gsi=ai⊙bi ,则式(1)可以改写为si= gsi⊙ci ,先考察第一组CLA s0=gs0⊙c0 s1=gs1⊙c1=gs1⊙(g0+p0c0)? s2=gs2⊙c2=gs2⊙(g1+p1g0+p1p0c0)? s3=gs3⊙c3=gs3⊙(g2+p2g1+p2p1g0+p2p1p0c0) 因为g, p的值只有“00”、“01”、“11”这三种组合,结合布尔代数性质A⊙0=、A⊙1=A可知,s3的值最终可以归结为3个表达式:gs3, 3和(gs3⊙c0),同样,s2值的3个表达式为gs2, 2和(gs2⊙c0),s1为gs1, 1和(gs1⊙c0)。

于是式(8)至式(11)就可以化为 s0=c0(gs0)+ 0 (0) (12) s1=c0(gs1⊙p0)+0(gs1⊙g0) (13) s2=c0(gs2⊙(g1+p1p0))+ 0 (gs2⊙(g1+p1g0))(14) s3=c0(gs3⊙(g2+p2g1+p2p1p0)) +0(gs3⊙(g2+p2g1+p2p1g0)) (15) 其他组,如s4~s7、s8~s11等,情况和s0~s3一样。

参考资料来源:百度百科-加法器

求四位全加器原理!?

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY full4 IS --4位全加器 PORT(A0,A1,A2,A3:IN STD_LOGIC; B0,B1,B2,B3:IN STD_LOGIC; Ci:IN STD_LOGIC; S0,S1,S2,S3:OUT STD_LOGIC; Co:OUT STD_LOGIC); END full4; ARCHITECTURE one OF full4 IS COMPONENT full --元件例化 PORT(a,b,ci:IN STD_LOGIC; s,co:OUT STD_LOGIC); END COMPONENT; SIGNAL D,E,F:std_logic; BEGIN U0:full PORT MAP(A0,B0,Ci,S0,D); U1:full PORT MAP(A1,B1,D,S1,E); U2:full PORT MAP(A2,B2,E,S2,F); U3:full PORT MAP(A3,B3,F,S3,Co); END one; LIBRARY IEEE; --1位全加器 USE IEEE.STD_LOGIC_1164.ALL; ENTITY full IS PORT(a,b,ci:IN STD_LOGIC; s,co:OUT STD_LOGIC); END full; ARCHITECTURE one OF full IS BEGIN s<=a xor b xor ci; co<=(a and b) or (a and ci) or (b and ci); END one;

- 并行加法器求四位全加器原理!?相关文档

- 并行加法器利用加法器设计一个代码转换电路,将bcd代码的8421码转换成余3码

- 并行加法器加法器原理

- 并行加法器什么是并行进位

- 并行加法器用两个4位并行加法器和适当的逻辑门电路实现(X+Y)×Z

Hosteons:新上1Gbps带宽KVM主机$21/年起,AMD Ryzen CPU+NVMe高性能主机$24/年起_韩国便宜服务器

我们在去年12月分享过Hosteons新上AMD Ryzen9 3900X CPU及DDR4内存、NVMe硬盘的高性能VPS产品的消息,目前商家再次发布了产品更新信息,暂停新开100M带宽KVM套餐,新订单转而升级为新的Budget KVM VPS(SSD)系列,带宽为1Gbps端口,且配置大幅升级,目前100M带宽仅保留OpenVZ架构产品可新订购,所有原有主机不变,用户一直续费一直可用。Bud...

LiCloud:香港CMI/香港CN2+BGP服务器,30Mbps,$39.99/月;香港KVM VPS仅$6.99/月

licloud怎么样?licloud目前提供香港cmi服务器及香港CN2+BGP服务器/E3-1230v2/16GB内存/240GB SSD硬盘/不限流量/30Mbps带宽,$39.99/月。licloud 成立於2021年,是香港LiCloud Limited(CR No.3013909)旗下的品牌,主要提供香港kvm vps,分为精简网络和高级网络A、高级网络B,现在精简网络和高级网络A。现在...

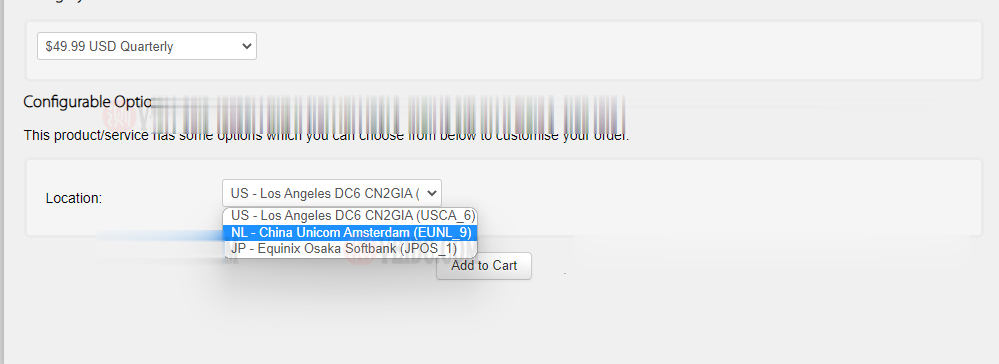

搬瓦工:新增荷兰机房 EUNL_9 测评,联通 AS10099/AS9929 高端优化路线/速度 延迟 路由 丢包测试

搬瓦工最近上线了一个新的荷兰机房,荷兰 EUNL_9 机房,这个 9 的编号感觉也挺随性的,之前的荷兰机房编号是 EUNL_3。这次荷兰新机房 EUNL_9 采用联通 AS9929 高端路线,三网都接入了 AS9929,对于联通用户来说是个好消息,又多了一个选择。对于其他用户可能还是 CN2 GIA 机房更合适一些。其实对于联通用户,这个荷兰机房也是比较远的,相比之下日本软银 JPOS_1 机房可...

并行加法器为你推荐

-

蓝屏代码电脑蓝屏,出现代码。diskgenius免费版DiskGenius恢复文件是免费的吗横幅广告通栏广告 横幅广告是什么意思碰撞球碰撞分为哪几种,分别解释一下spinmaster手指滑板品牌空间图片空间图片比特币官方客户端如何查询比特币、莱特币确认 ?snoopy官网SNOOPY护肤品究竟是国内生产的吗?在哪生产的?微信备份通讯录在哪微信通信录备份在哪goldwave教程如何利用GoldWave --来剪切一个完整的音乐?